# Artificially Intelligent Dynamic Pattern Recognition

### Soo-Dong Lee

Department of Electrical Engineering and Electronics (Received December 30, 1981)

### (Abstrract)

This paper presents new results estimated with a multicategory classification system which consists of a randomly fed back digital learning net and single-layer nets, including decision feedback loops between them.

The system behaves "intelligen ly" not only in the sense that it clusters incoming stimuli on the basis of its internal states but also because it adjusts its decisions continuously until a stable strong decision is obtained.

## 人工知能에 의하 패턴의 動的 認識

李 秀 東 電氣 및 電子工學科 (1981, 12, 30 접수)

#### 〈요 약〉

본 논문에서는 랜턴·피드백 루프를 가지는 디지탈학습망(Digital Learning Net)과 단흥망군(Single-layer Nets)사이에 판정·피드백 루프를 두어 다범주판정시스템(Multi-category Classification System)을 구성하고, 예측되는 새로운 결과를 밝혔다.

위의 시스템은 외부입니을 내부상대에 의거하여 찬독한 뿐만 아니라 친독한 결과를 안정상대에 이드도록 끊임없이 보정하는 '지능'을 가지고 동작한다.

#### 1. Introduction

In the field of pattern recognition, much effort has been devoted to the development of digital learning nets which behave with "intelligence". However the area in which a contribution has been lacking is that of a multicategory classifier which makes a strong decision at its output within a few cycles.

A multi-category classifier such as the singlelayer nets<sup>1</sup> makes a marginal decision by detecting the strongest response amongst responses of each descriminator, but when a distinction is required between two sets of patterns which differ only by a small amount, the margin between these two decisions become very narrow. That is, context effects which make recognition possible despite an ambiguous input have been excluded in the nets. In order to bring context effects into the system, we must include a feedback mechanism that provides information about previous recognitions to be used when it comes to recognising the present stimulus.

An OR-ed feedback net, 2-5 where an external

input is imposed by OR-ing it with the feedback wires carrying the previous output states, clusters incoming information on the basis of forming internal models. But it suffers from domination of last seen patterns. The "aging" process allows the net to become gradually less sensitive to its teach terminals by removing teach clock signal from an ever increasing number of elements, thus can reduce the domination of last-seen patterns. But the performance of the net will be affected by choosing different teach terminals during the process, that is, the feedback connections can not be determined before training the net, and this goes legged the nature of training.

A decrean feedback net such as the action-oriented learning net<sup>(6)</sup> makes a strong decision at its output by amplifying the desired responses. The output of the net is fed back to particular inputs of RAMs (random-access memories) within the net so that the net awares of 1.8 own decisior. But for some ambiguous inputs, it needs several cycles for the net to enter the stable states from which the final decision is made, and the net is restricted to perform two-way classifications.

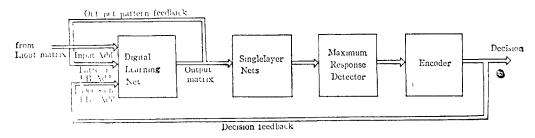

In this paper, a multi-category classification system shown in Fig. 1 is proposed and investigated to see whether it can be trained to make a strong decision within a limited cycle. The system and the action-oriented learning net are like each other in using the decision feedback, but differ widely in the sense that the system enters into the stable

states by "cleaning up" the variations of an external input pattern from the prototype pattern which is selected by previous decisions, while the action-oriented learning net enters into the stable states by amplifying the desired responses.

For multi-category classifications in the system, the problem arising is how the "cleanup" processes and the decision processes can operate fast enough with confidence for an unknown input pattern.

The training is the key in solving this problem. The system consists of the digital learning net providing the preprocessing for an external input pattern and the single-layer nets making a decision from the preprocessed pattern. The address of each RAM in the digital learning net is partitioned into three groups. The digital learning net is trained to produce a prototype pattern on the output matrix by applying a set of training patterns as well as their corresponding prototype pattern and a category information on the input matrix, output matrix and the decision address terminals of each RAM respectively.

After training, a set of training patterns and a prototype pattern are chosen by the previous decision and are compared to an external input pattern during the "clean-up" process of the digital learning net. Then the irregularities of the external input pattern are enforced to be cleaned up to bring it into a more prototype-like pattern, that is, the external input pattern is preprocessed by pre-

Fig.1 Block diagram of system

comparison. Thus the single-layer nets which are required to make decisions on the preprocessed output pattern of the digital learning net can make a strong decision without any confusion.

This process would greatly reduce the number of training patterns at the single-layer nets, therefore each descriminator of the nets is trained by a prototype pattern corresponding to the category. This is probably the case in long term memory (LTM).

The decision information for the digital learning net is obtained through the feedback loop between the overall output of the single-layer nets and the decision feedback address terminals of the digital learning net. The existance of this long feedback loop plays an important role in the development of its "intelligence", and through the action of this feedback loop, the system can learn without the sequencing effects of multicategory training

patterns and can recognise an external input pattern within a limited cycle with an appropiate prototype pattern.

This is probably the case in the human brain, according to the prototype-hypothesis of pattern recognition, (7) we remember any object by its prototype rather than by its whole template and recognise the object by comparing it to the prototypes stored in long term memory, and then adjust the decision repeatedly until we are satisfied that we have identified the object.

## II. Net Structure-Hardware Design

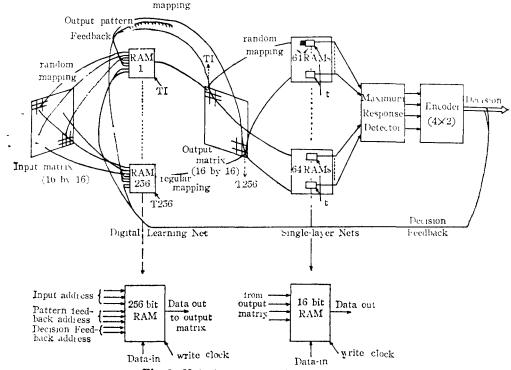

The overall net structure and the hardware connections of the proposed system are shown in Fig. 2. The design is centered around RAMs, but this scheme is rather conceptual approach because the embodiment of the resulting system might turn out to be a specialised micropro-

Fig. 2 Net structure of the system

cessor system or straight forward read-only memory (ROM) programmable logic array hardware. The essential elements and the descriptions of the system are defined as follows.

Digital learning net (DLN): This net consists of 256 RAMs, and each 256-bits RAM has eight address terminals. These address terminals are partitioned into three groups, that is, three input address terminals, three output pattern feedback address terminals and two decision feedback address terminals. In addition to these address terminals, each RAM has single data-in terminal (teach terminal) and single data-out terminal.

Input matrix (I): The input patterns appear on thir 16 by 16 binary matrix. Each element of the I matrix is connected to three randomly chosen elements of the X matrix in such a way that no  $x_{\cdot k}$ , that is, j-th input of the k-th RAM  $(1 \le j \le 3, 1 \le k \le 256)$ , is connected to more than one element of I.

Mapped input matrix (X): This 3 by 256 binary matrix is connected to the input address terminals of each RAM in such a way that no two of the X elements connected to the same element of I belong to the same RAM.

Output matrix (Z): Each output of the RAMs generates this 16 by 16 binary matrix whose ordering is regular. Each element of the Z matrix is connected to three, randomly chosen elements of the O matrix in such a way that no  $O_{1k}$ , that is, (3+j)th input of the k-th RAM  $(1 \le j \le 3, 1 \le k \le 256)$ , is connected to more than one element of Z.

Mapped output matrix (O): This 3 by 256 binary matrix is connected to the pattern feedback address terminals of each RAM in such a way that no two the O elements connected to the same element of Z belong to the same RAM.

Training matrix of  $DLN(T_L)$ : This is an additional 16 by 16 matrix which consists of

the teach inputs of the RAMs.  $T_L$  is obtained from Z by regular mapping.

Single-layer net (SLN): This net consists of 64 RAMs, and each 16-bits RAM has four address terminals. The address of each RAM is chosen from Z matrix by random onto mapping. The teach inputs of this net are all set to 1 during training on appearance of training patterns at Z matrix.

Single-layer nets (SLNs): The nets consist of four descriminators, a maximum response detecter and an encoder. The response of each descriminator is supplied to the maximum response detecter which assigns the classification to that descriminator which has the strongest response. The output of the maximum response detector is encoded into two bits binary number, and this encoded decision is fed back to the decision feedback address terminals of the digital learning net.

## II. Training

Before any training is carried out, all the RAM bit stores are initialised, that is, all patterns applied on the input matrix produce an all Os state pattern for all initial states of the RAMs array.

Training is entered by generating the input addresses of the RAMs in the array and applying a training pattern to the corresponding data-in terminals. These training data are then clocked into the RAMs so that the next state of the array forms the training pattern, that is, the addressed store location of each RAM change its value to that of the corresponding data-in terminal. Now if the training pattern is clocked again, a transition from the state pattern back to itself is enforced (i.e., stable-state creation).

When variable training patterns are introduced into the input matrix, the response to the unknown pattern is more like prototype pattern is more like prototype pattern which is considered to consist of the features common to all instances of a pattern.

The concept of training the proposed system is based on the prototype-hypothesis of pattern recognition. Human beings remember any object by its prototype, what are stored in long-term memory (LTM) are prototypes—central, ideal representatives of sets of stimuli, and in theory any stimulus can be encoded as a prototype plus a list of variations. The incoming stimuli can then be compared to prototypes rather than templates.

#### 1. Training of Digital Learning Net

The training procedure of the digital learning net is as follows. At first, the training patterns belonging to one category are supplied on the I matrix, and the category information is provided to each decision feedback address terminals of the RAMs. The feedback from the Z matrix is set so that all the data-out terminals of the RAMs form the prototype pattern belonging to that category. The net is then trained to generate the prototype pattern at the Z matrix by applying the prototype pattern to its  $T_L$  matrix. That is, the training consists of setting those addressed store locations to is only in those RAMs that have corresponding is in the data-in terminals.

The effect of this type of training is to create the same stable, re-entrant state for all input patterns in the training set. There is no sequencing effect during training, that is, the training for one class does not alter the effect of the previous training for another classes, this dues to the fact that the decision feedback address partitions the array of RAMs into non-overlapping areas.

After training, the digital learning net "percepts" the prototype patterns, that is, the cotents of the store locations addressed by both training patterns and their corresponding prototype patterns are set with the prototype

patterns during training. The "perception" is defined as the entry into specific areas being determined by the classes of input patterns to which the net is exposed during training.

#### 2. Training of Single-layer Nets

The single-layer nets in the proposed system are trained only on the prototype patterns, that is, each descriminator in the nets is trained individually on a prototype pattern from which the category is detected. The training proceeds as follows.

All the memories in the single-layer nets are initially set to zero, and a training (prototype) pattern is shown at the Z matrix which provides the 4-tuple input addresses for the corresponding descriminator. Then the descriminator is trained with all is at the data-in terminals to output all is at the data-out terminals of the RAMs. That is, all the addressed store locations are set to is.

During recognition, if a pattern on the Z matrix belongs to one of the training (prototype) patterns, the corresponding descriminator outputs its maximum response (i.e., 64). Generally a decision is made about which the single-layer nets match best, and the pattern is recognised as corresponding to the contents that are stored in the single-layer nets.

The decision made at the output of the nets is encoded into two bits binary number and fed back to each decision feedback address terminals of the digital learning net to adjust the decision it provides and to classify the output pattern it descriminates for the recognition that follows.

This type of training provides the comparison function for the system, and enforces the system to make a strong decision within limited cycles.

## II. Software Design

The hardware design shown in Fig. 2 is

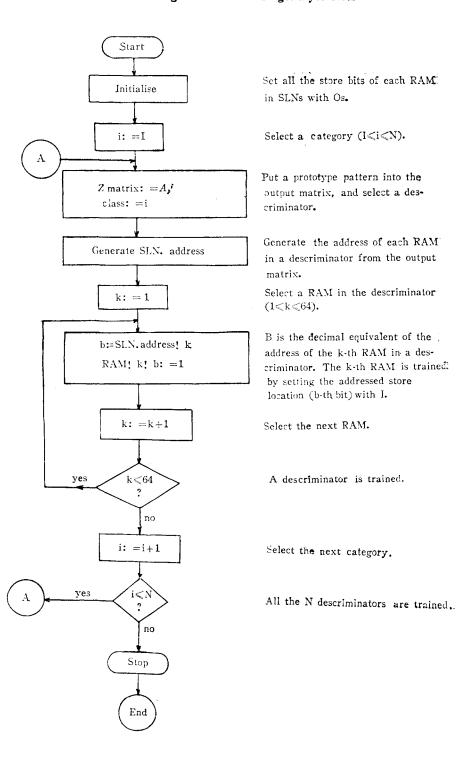

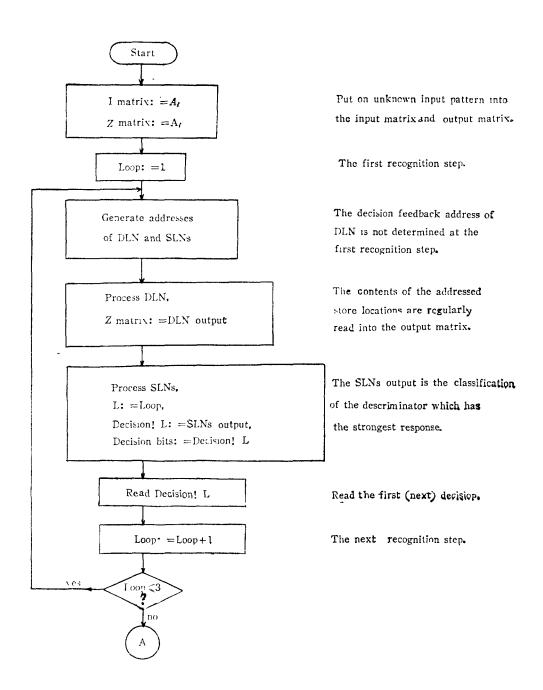

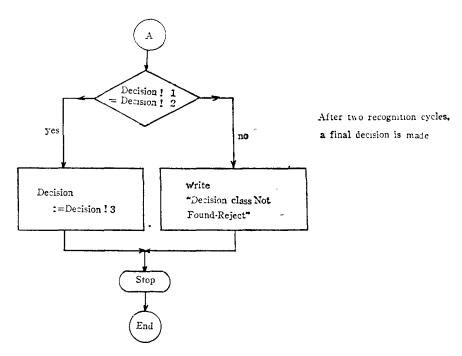

focused on the behaviour of a RAM as an element of adaptive logic circuits, but this design might easily turn out to be software for conventional digital computers. In this section, the software design scheme for the proposed system is discussed by showing overall flow charts as follows.

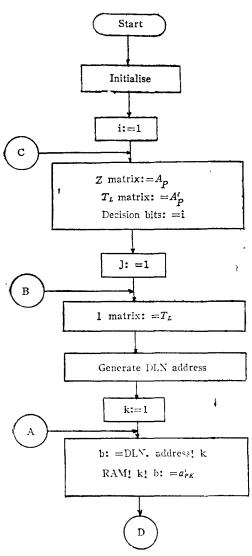

**V-1.** The training procedure of the digital learning net

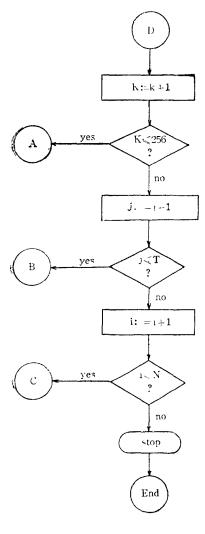

**V**-3. The recognition procedure of an unknown pattern

## 1. Training Procedure of The Digital Learning Net

Set all the store bits of each RAM with Os.

Select a Category ( $I \le i \le N$ ).

Put a Prototype Pattern into the ouput matrix and the training matrix.

Put a category information into the decision bits of SLNs.

Select a training pattern belonging to a category ( $I \le J \le T$ )

Put the training pattern into the input matrix.

Generate DLN. address from X matrix, O matrix and decision bits.

Select a RAM in the DLN (I $\leq$ k $\leq$ 256).

B is the decimal equivalent of the address of the k-th RAM.

The k-th RAM is trained by setting the addressed store location with the contents of the k-th element of T<sub>L</sub>.

Select the next RAM.

A training pattern  $T_{J}$  and a prototype pattern  $A_{J}$  are percepted.

Select the next training pattern.

All the Training patterns in T and a prototype pattern  $A_{\mu}^{i}$  are percepted.

Select the next category.

All the TXN training patterns in T and all N prototype patterns in Ap are percepted.

### 2. Training Procedure of Single-tayer Nets

## 3. Recognition Procedure of an Unknown Pattern

#### V. Conclusions

The expected results which has been investigated after training are as follows.

- 1) The training procedure creates stablestates directly related to an unknown input pattern.

- ii) Each descriminator is not required to accept a set of training patterns but a prototype pattern.

- iii) The ststem provides preprocessing for an unknown input pattern during recognition cycles, and the output pattern generated on the output matrix is a prototype-like pattern related to the input pattern.

- iv) A strong decision can be made, and when an unknown input pattern is too ambiguous to make a decision, a clear rejection occurs.

- v) The system can be extended to any multicategory system by adding descriminators to the single-layer nets, and increasing decision

feedback address terminals of each RAM in the digital learning net on the expense of hardware.

#### References

- I. Aleksander, and T. J. Stonham, "Guide to pattern recognition using random-access memories", Computers and Digital Techniques, Feb. 1973, vol. 2, No. 1.

- I. Aleksander, and E.H. Mamdan, "Microcircuit learning nets: improved recognition by means of pattern feedback", Electron. Lett., 1968, 4, pp. 425-426.

- M.C. Fairhurst, and I. Aleksander, "Natural pattern clustering in digital learning nets', Electron. Lett., 1971, 7, pp. 724-726

- 4. M.C. Fairhurst, and I. Aleksander, "Dynamics of the perception of patterns in random learning nets", in "Machine Perception of Patterns and Pictures", p. 311, Institute of Physics, London, June 1972.

- 5. I. Aleksander, T. J. Stonham, and M. J. D.

Wilson, "Adaptive logic for artificially intelligent systems", The Radio and Electronic Engineer, Vol.44, No.1, January 1974.

- 6. I. Aleksander, "Action-oriented learning

- networks", Kybernetes, 1975, 4, pp. 39-44.

- Klatzky Roberta L., "Human Memory: Structures and Processes", W. H. Freeman and Company, 1975.