### 저작자표시-비영리-변경금지 2.0 대한민국

### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

Disclaimer 🖃

# **Doctor of Philosophy**

# Optimization of GaN-Based High-Electron-Mobility Transistors (HEMTs) for High-Frequency Applications: A Comprehensive Study on Reliability and Performance Enhancement

The Graduate School

of the University of Ulsan

Department of Electrical,

Electronic and Computer Engineering

Walid Amir

# Optimization of GaN-Based High-Electron-Mobility Transistors (HEMTs) for High-Frequency Applications: A Comprehensive Study on Reliability and Performance Enhancement

Supervisor: Prof. Sunghwan Kim

### A Dissertation

Submitted to

the Graduate School of the University of Ulsan

In partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

by

Walid Amir

Department of Electrical,

Electronic and Computer Engineering

University of Ulsan, Korea

February 2024

# Optimization of GaN-Based High-Electron-Mobility Transistors (HEMTs) for High-Frequency Applications: A Comprehensive Study on Reliability and Performance Enhancement

This certifies that the dissertation of

Walid Amir is approved.

Committee Chair, Dr. Hyeon Cheol Kim

Committee Member, Dr. Sunghwan Kim

Committee Member, Dr. Tae-Woo Kim

Committee Member, Dr. Jaehyun Park

Committee Member, Dr. Hyuk-Min Kwon

Department of Electrical,

Electronic and Computer Engineering

University of Ulsan, Korea

February 2024

# Optimization of GaN-Based High-Electron-Mobility Transistors (HEMTs) for High-Frequency Applications: A Comprehensive Study on Reliability and Performance Enhancement

By

### Walid Amir

Submitted to the Graduate School of the University of Ulsan

In partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

### **ABSTRACT**

The widespread application of GaN-based high electron mobility transistors (HEMTs) in high-frequency and high-power applications still faces reliability instability. Achieving the necessary reliability is a challenging problem, primarily attributed to the elevated operational voltage and material properties. To enhance reliability, it is crucial to develop a comprehensive physical understanding of the underlying degradation mechanisms. This comprehensive thesis undertakes an in-depth exploration of trapping-related degradation in AlGaN/GaN high electron mobility transistors (HEMTs), extending and refining prior research on structural issues. The investigation encompasses a multi-faceted approach, beginning with a thorough characterization of interface and border traps using frequency-dependent C-V and G-V methods. The study then explores the influence of Al composition in AlGaN barriers on device performance, revealing insights into trap densities and their implications. A novel aspect of the research involves the application of O<sub>2</sub> plasma treatment to mitigate volume trap states, showcasing improvements in Schottky characteristics and microwave performance. Additionally, the thesis provides a thorough analysis of Positive-Bias-Temperature Instability (PBTI) and the impact of channel back-barrier and channel thickness scaling, explaining the intricate relationship between these factors. Overall, this research significantly advances our understanding of trapping effects in AlGaN/GaN HEMTs, proposing innovative strategies to enhance device reliability and performance across various operational conditions.

# **TABLE OF CONTENTS**

| Cha | pter 1: | Introduction                                                             |    |

|-----|---------|--------------------------------------------------------------------------|----|

| 1.1 | III-V C | compound Semiconductor                                                   | 09 |

| 1.2 | GaN H   | igh Electron Mobility Transistors                                        | 10 |

| 1.3 | Motiva  | tion                                                                     | 12 |

| 1.4 | Objecti | ves                                                                      | 14 |

| 1.5 | Thesis  | outline                                                                  | 14 |

| Cha | pter 2: | Fundamentals of GaN HEMTs                                                |    |

| 2.1 | GaN m   | aterial properties                                                       | 16 |

| 2.2 | AlGaN   | /GaN High Electron Mobility Transistors                                  | 19 |

| 2.3 | Substra | ites                                                                     | 21 |

| 2.4 | Failure | Mechanism                                                                | 22 |

|     | 2.4.1   | Inverse Piezoelectric Effect and Thermo-mechanical Strain                | 23 |

|     | 2.4.2   | Time-Dependent Breakdown of the AlGaN/GaN Structure and Dielectrics      | 24 |

|     | 2.4.3   | Electro-chemical GaN Oxidation                                           | 24 |

|     | 2.4.4   | Hot Electron Effects                                                     | 25 |

|     | 2.4.5   | Trapping Phenomena                                                       | 27 |

|     | 2.4.6   | Reliability                                                              | 27 |

| 2.5 | Summa   | ury                                                                      | 29 |

| Cha | pter 3: | Experimental setup                                                       |    |

| 3.1 | Introdu | ction                                                                    | 30 |

| 3.2 | Device  | s and fabrication processes                                              | 30 |

| 3.3 | Reliabi | lity Analysis Methods                                                    | 34 |

|     | 3.3.1   | Interface Trap Density $(D_{it})$ Extraction                             | 34 |

|     | 3.3.2   | Border Trap Density $(N_{bt})$ Extraction                                | 36 |

|     | 3.3.3   | Volume Trap Density $(N_t)$ Extraction with $1/f$ noise characterization | 38 |

|     | 3.3.4   | Single Short Pulse I-V characterization technique                        | 39 |

|     | 3.3.5   | Stress Characterization Methodology                                      | 41 |

| 3.4 | Summa   | ary                                                                      | 42 |

| Cha | pter 4: | Interfacial Traps in AlGaN/GaN HEMTs                                     |    |

| 4.1 | Introdu | ction                                                                    | 43 |

| 4.2 | Defect  | sites in the AlGaN/GaN interface                                         | 44 |

| 4.3 | Experir | mental details for the interfacial trap analysis                         | 46 |

| 4.4 | Extract | ion of interface trap densities $(D_{it})$                               | 47 |

| 4.5               | Extrac                                                      | tion of border trap densities $(N_{bt})$                                 | 50  |

|-------------------|-------------------------------------------------------------|--------------------------------------------------------------------------|-----|

| 4.6               | Reliability Validation of the extracted $D_{it}$ & $N_{bt}$ |                                                                          | 52  |

| 4.7               | Summ                                                        | ary                                                                      | 54  |

| Cha               | pter 5:                                                     | Impact of various Al compositions in Reliability Assessment              | of  |

| Al <sub>x</sub> C | Ga <sub>1-x</sub> N/                                        | GaN HEMTs                                                                |     |

| 5.1               | Introdu                                                     | action                                                                   | 55  |

| 5.2               | Electro                                                     | on Trapping phenomenon during device operation                           | 56  |

| 5.3               | Charge                                                      | e-Trapping Analysis with Pulsed I-V                                      | 58  |

| 5.4               | Charge                                                      | e-Trapping Analysis with Constant Voltage Stress Condition               | 60  |

| 5.5               | Quanti                                                      | tative Analysis of Trap Density                                          | 61  |

| 5.6               | Microv                                                      | wave properties                                                          | 66  |

| 5.7               | Summ                                                        | ary                                                                      | 67  |

| Cha               | pter 6:                                                     | Effects of O <sub>2</sub> Plasma treatment on Trap states                |     |

| 6.1               | Introdu                                                     | action                                                                   | 69  |

| 6.2               | O <sub>2</sub> Pla                                          | sma Treatment Technology                                                 | 69  |

| 6.3               | Surfac                                                      | e morphology                                                             | 71  |

| 6.4               | DC ch                                                       | aracteristics                                                            | 73  |

| 6.5               | Pulsed                                                      | I-V and Charge Trapping Analysis                                         | 74  |

| 6.6               | RF Ch                                                       | aracteristics Analysis                                                   | 77  |

| 6.7               | Summ                                                        | ary                                                                      | 82  |

| Cha               | pter 7:                                                     | Trapping effects due to Hot electrons                                    |     |

| 7.1               | Introdu                                                     | action                                                                   | 83  |

| 7.2               | Chann                                                       | el Back Barrier Technology                                               | 83  |

|                   | 7.2.1                                                       | "Hot Electron trapping" mechanism                                        | 84  |

|                   | 7.2.2                                                       | PBTI Degradation and V <sub>T</sub> Shift Kinetics                       | 87  |

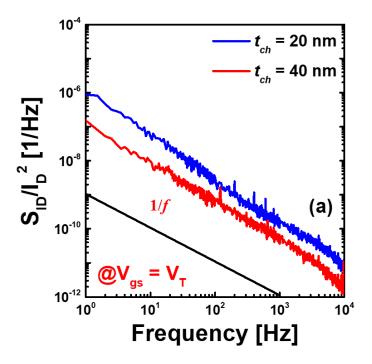

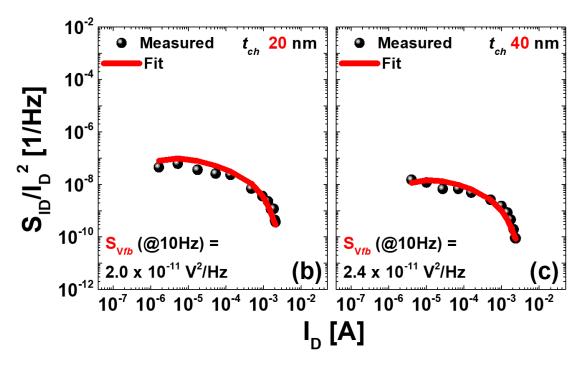

|                   | 7.2.3                                                       | Low-Frequency Noise characteristics                                      | 91  |

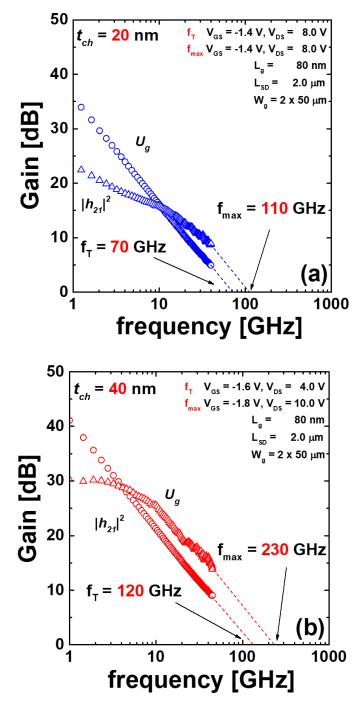

|                   | 7.2.4                                                       | RF Characteristics Analysis                                              | 92  |

| 7.3               | Chann                                                       | el thickness scaling technology                                          | 94  |

|                   | 7.3.1                                                       | PBTI Degradation and V <sub>T</sub> Shift Kinetics                       | 95  |

|                   | 7.3.2                                                       | Low-Frequency Noise characteristics                                      | 97  |

|                   | 7.3.3                                                       | RF Characteristics Analysis                                              | 98  |

| 7.4               | Summ                                                        | ary                                                                      | 100 |

| Cha               | pter 8:                                                     | Conclusion                                                               |     |

| 8.1               | Summ                                                        | ary                                                                      | 101 |

| 8.2               | Recom                                                       | nmendations for enhancing device performance and maintaining reliability | 105 |

| 8.3               | Sugge                                                       | stions for future work                                                   | 106 |

# LIST OF FIGURES

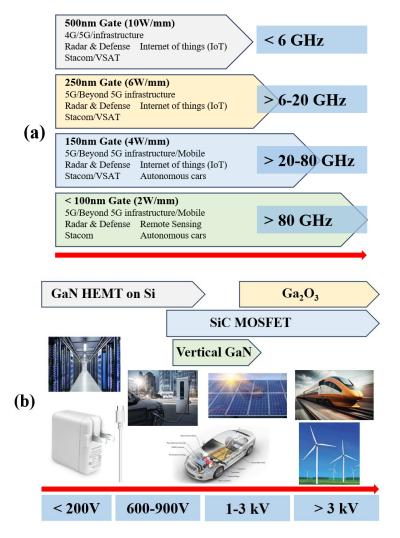

| Figure 1-1 | (a) A technology roadmap for RF GaN HEMTs. (b) A technology roadmap for Power GaN HEMTs.         | 11 |

|------------|--------------------------------------------------------------------------------------------------|----|

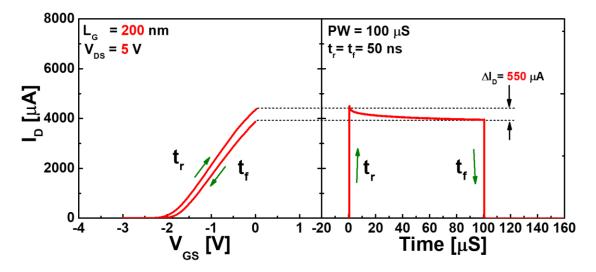

| Figure 1-2 | Pulsed $I_D$ vs $V_{GS}$ and $I_D$ vs. pulse time showing $\Delta I_D$ degradation due to charge | 12 |

|            | trapping.                                                                                        |    |

| Figure 2-1 | Comparison of GaN material merits to Si and GaAs.                                                | 18 |

| Figure 2-2 | (a) the Ga-polar GaN crystal structure and (b) the presence of spontaneous and                   | 20 |

|            | piezoelectric polarization within the Ga-polar system, featuring the 2DEG                        |    |

|            | situated at the lower AlGaN/GaN interface.                                                       |    |

| Figure 2-3 | The energy band diagram and charge distribution illustration of a Ga-polar                       | 21 |

|            | AlGaN/GaN HEMT in its unbiased state.                                                            |    |

| Figure 2-4 | Illustrative diagram depicting the primary mechanisms influencing the                            | 23 |

|            | reliability of GaN-based High Electron Mobility Transistors (HEMTs).                             |    |

| Figure 2-5 | Schematic cross-section of an AlGaN/GaN HEMT illustrating potential                              | 26 |

|            | consequences of hot electrons: these electrons have the potential to be captured                 |    |

|            | at interfaces, within the GaN buffer, on the surface, or within passivation                      |    |

|            | layers.                                                                                          |    |

| Figure 3-1 | Cross-section schematic of (a) Optical Trapezoidal-shaped gate. (b) EBL "T"                      | 31 |

|            | shaped gate.                                                                                     |    |

| Figure 3-2 | Layout of the reliability chip used in this work.                                                | 33 |

| Figure 3-3 | Equivalent circuit diagram representing metal-insulator-semiconductor                            | 34 |

|            | structure in depletion mode.                                                                     |    |

| Figure 3-4 | Equivalent circuit representing distributed bulk-oxide trap model.                               | 36 |

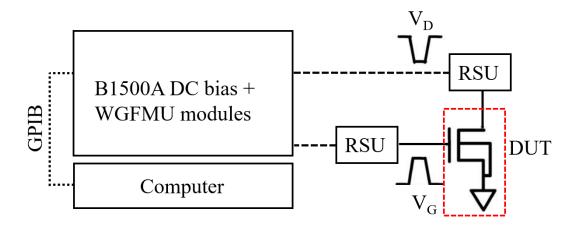

| Figure 3-5 | Experimental setup for the ultrashort pulsed I-V measurement.                                    | 40 |

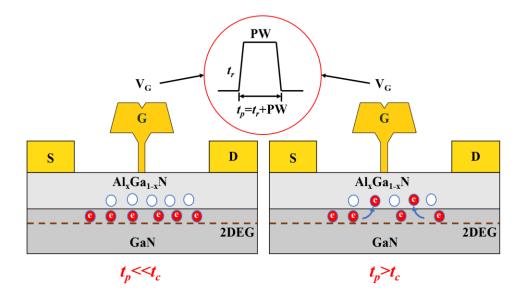

| Figure 3-6 | Schematic for the electron-trapping process during the pulsed I-V                                | 40 |

|            | measurements.                                                                                    |    |

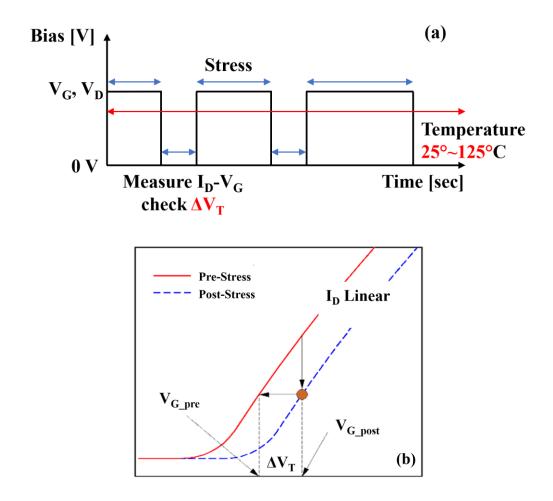

| Figure 3-7 | (a) Stress characterization Procedure used in this study (b) Threshold voltage                   | 41 |

|            | shift analysis with stress characterization.                                                     |    |

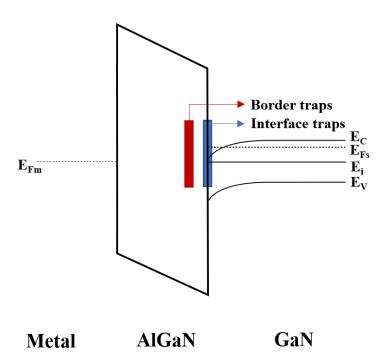

| Figure 4-1 | Band diagram illustration of AlGaN/GaN HEMT showing interface and border                         | 44 |

|            | trap sites.                                                                                      |    |

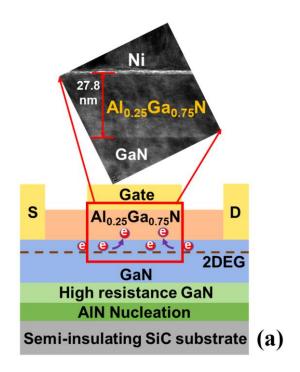

| Figure 4-2 | (a) Schematic cross-section and high-resolution TEM image of                                     | 45 |

|            | Al <sub>0.25</sub> Ga <sub>0.75</sub> N/GaN device. (b) Results of frequency-dependent C–V       |    |

|            | measurements showing active response region of traps.                                            |    |

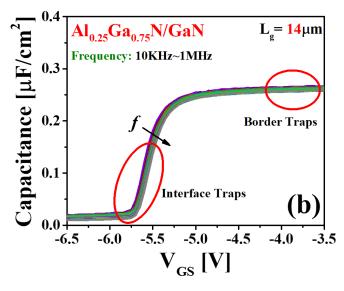

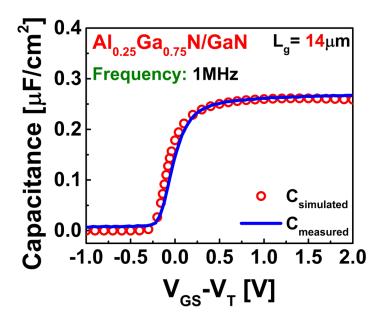

| Figure 4-3 | Comparison between measured and simulated C-V characteristics.                                   | 47 |

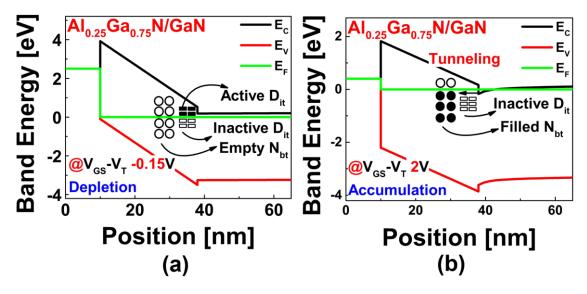

| Figure 4-4 | Simulated band diagram showing trap behavior (a) in depletion and (b) in                         | 48 |

|            | accumulation.                                                                                    |    |

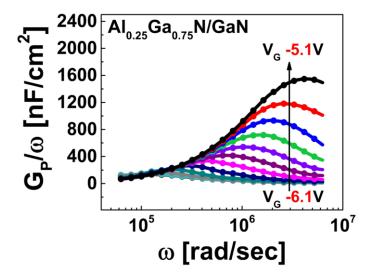

| Figure 4-5  | Equivalent parallel conductance $(G_P/\omega)$ with respect to frequency at different gate bias points.                    | 49 |

|-------------|----------------------------------------------------------------------------------------------------------------------------|----|

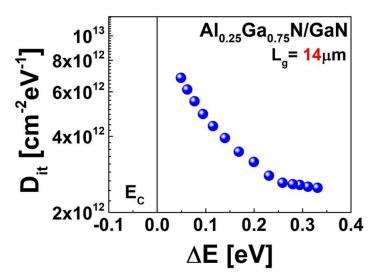

| Figure 4-6  | Distribution of interface traps as a function of band energy state.                                                        | 49 |

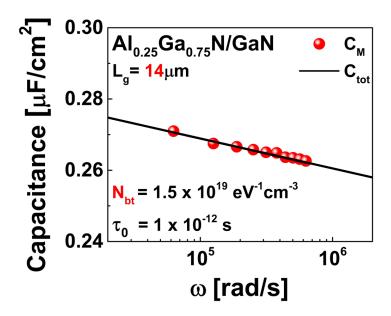

| Figure 4-7  | Fitting curves generated using a distributed circuit model at $V_{GS} = -3.5 \text{ V}$ .                                  | 51 |

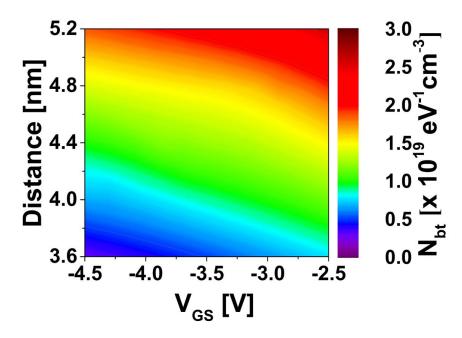

| Figure 4-8  | Contour mapping of border trap distribution in Al <sub>0.25</sub> Ga <sub>0.75</sub> N layer from                          | 51 |

| C           | Al <sub>0.25</sub> Ga <sub>0.75</sub> N/GaN interface.                                                                     |    |

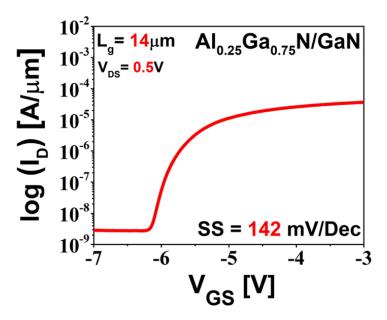

| Figure 4-9  | Transfer characteristics ( $log (I_D)$ – $V_{GS}$ ) showing SS of device.                                                  | 52 |

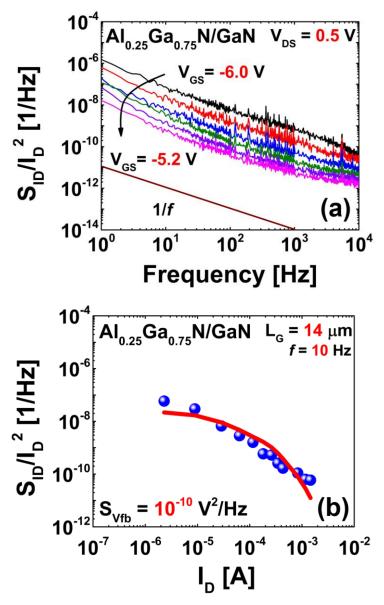

| Figure 4-10 | (a) Noise spectral density $(S_{ID}/I_D^2)$ with respect to frequency at various gate                                      | 53 |

|             | bias ( $V_{GS}$ ) points. (b) Noise spectral density ( $S_{ID}/I_D^2$ ) and ( $g_m/I_D$ ) <sup>2</sup> as functions        |    |

|             | of drain current $I_D$ .                                                                                                   |    |

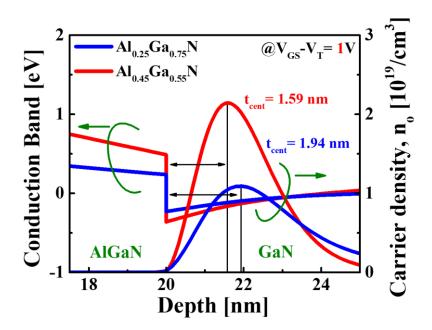

| Figure 5-1  | 1-D band $(E_c)$ simulation of the $Al_xGa_{1-x}N/GaN$ HEMTs including the carrier                                         | 56 |

|             | density profiles $(n_o)$ .                                                                                                 |    |

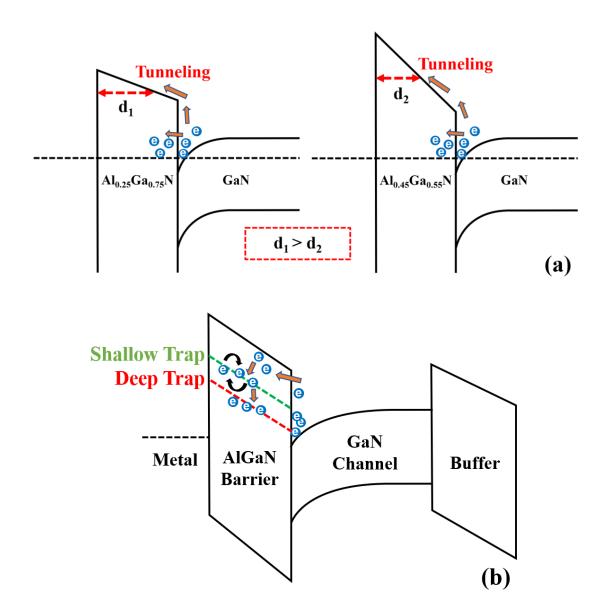

| Figure 5-2  | a) Illustration of the trapping behavior of channel electrons with varying Al                                              | 57 |

|             | composition (b) Schematic of the band diagram of $Al_xGa_{1-x}N/GaN$ HEMTs                                                 |    |

|             | defining the "Shallow" and "Deep" trap states that capture tunneling channel                                               |    |

|             | carriers.                                                                                                                  |    |

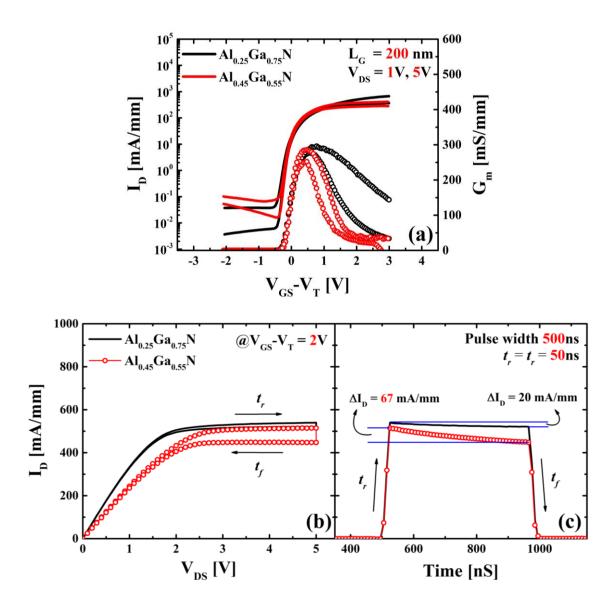

| Figure 5-3  | (a) DC transfer characteristics of the samples at $V_{DS} = 1$ , 5V with respect to the                                    | 59 |

|             | gate overdrive voltage $(V_{GS}-V_T)$ . (b) A single-pulse $I_D-V_D$ characteristics of                                    |    |

|             | AlGaN/GaN HEMTs with different Al compositions. (c) Rapid deterioration                                                    |    |

|             | of the drain current over time when a maximum pulse is applied to both gate                                                |    |

|             | and drain, which is consistent with the pulsed $I_D$ – $V_D$ sweep.                                                        |    |

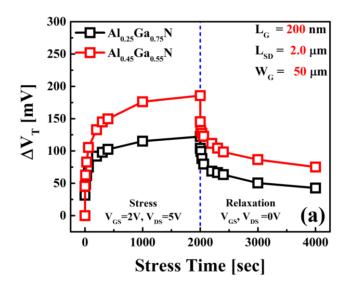

| Figure 5-4  | (a) Threshold voltage shift ( $\Delta V_T$ ) characteristics of AlGaN/GaN HEMTs during                                     | 60 |

|             | constant voltage stress at high drain bias ( $V_{DS} = 5$ V) condition illustrating                                        |    |

|             | charge-trapping and de-trapping properties of the channel electrons. (b) Power-                                            |    |

|             | law time dependency of the observed $\Delta V_T$ excluding the fast-transient charge-                                      |    |

|             | trapping components $(\Delta V_T - \Delta V_{T.initial (1 s)})$ in two samples.                                            |    |

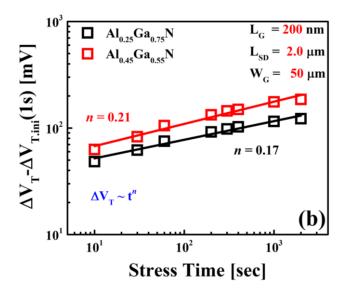

| Figure 5-5  | (a) Interface trap density $(D_{it})$ with respect to band energy with different Al                                        | 62 |

|             | compositions. (b) Histogram illustration of interface trap density $(D_{it})$ showing                                      |    |

|             | a reduction of 35% with reduced Al composition.                                                                            |    |

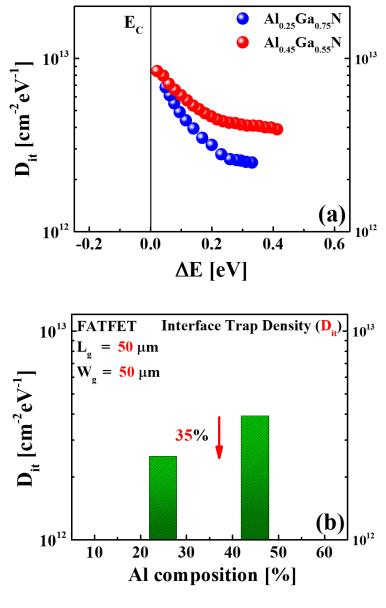

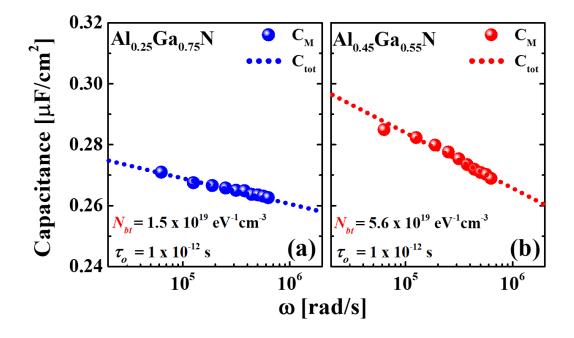

| Figure 5-6  | (a) Fitting curves of measured ( $C_M$ ) and calculated ( $C_{tot}$ ) capacitances at $V_{GS}$ -                           | 63 |

|             | $V_T = 1$ V, generated from the Distributed circuit model. (b) Border trap density                                         |    |

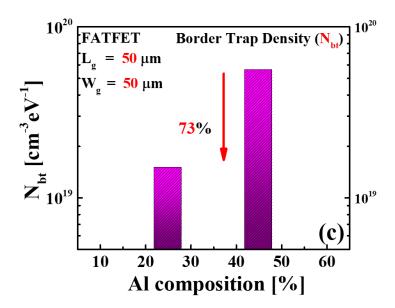

|             | $(N_{bt})$ with respect to different Al compositions shows a 73% reduction.                                                |    |

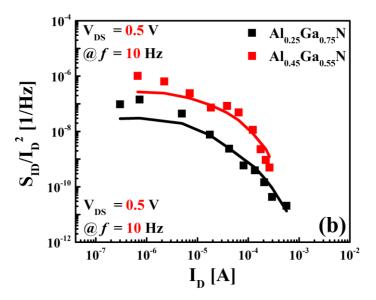

| Figure 5-7  | (a) Comparison of the normalized drain-current power spectral density (PSD)                                                | 65 |

|             | $(S_{ID}/I_D^2)$ at $V_{GS} = V_T$ and $V_{DS} = 0.5$ V. (b) Fitting curves of $S_{ID}/I_D^2$ values using                 |    |

|             | the CMF model calculated at a frequency of 10 Hz.                                                                          |    |

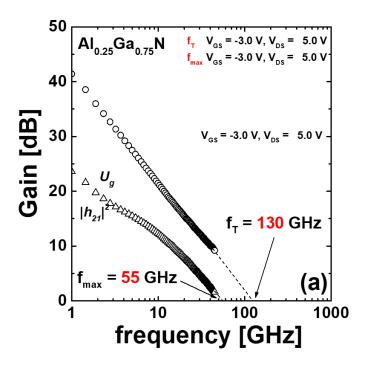

| Figure 5-8  | Measured RF Gains ( $ h_{2I} ^2$ , $U_g$ ) as a function of frequency, at near the peak $g_m$                              | 66 |

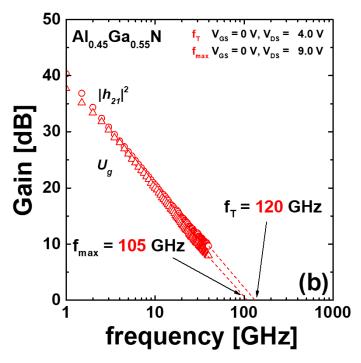

|             | bias conditions for (a) Al <sub>0.25</sub> Ga <sub>0.75</sub> N device (b) Al <sub>0.45</sub> Ga <sub>0.55</sub> N device. |    |

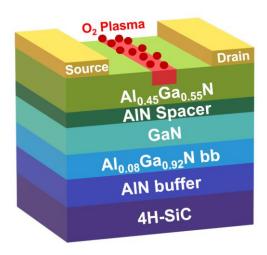

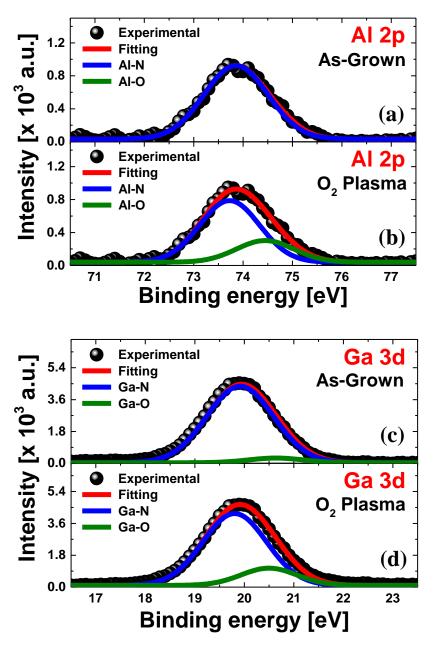

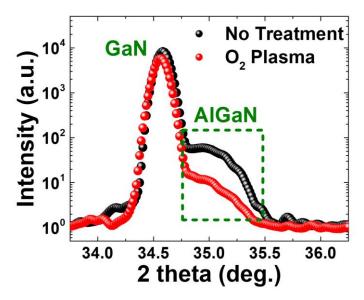

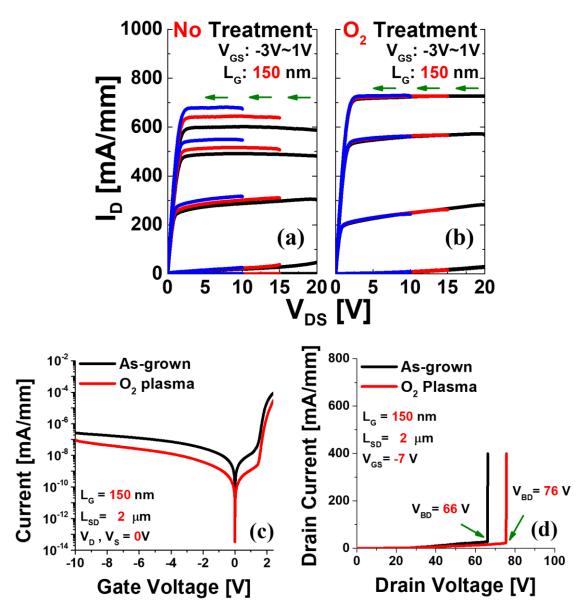

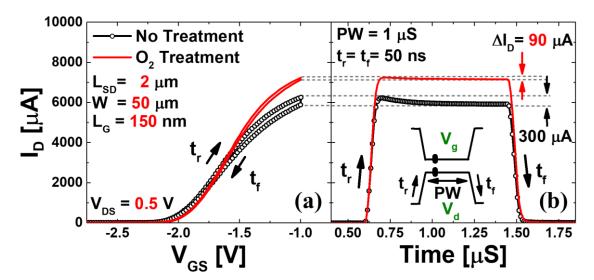

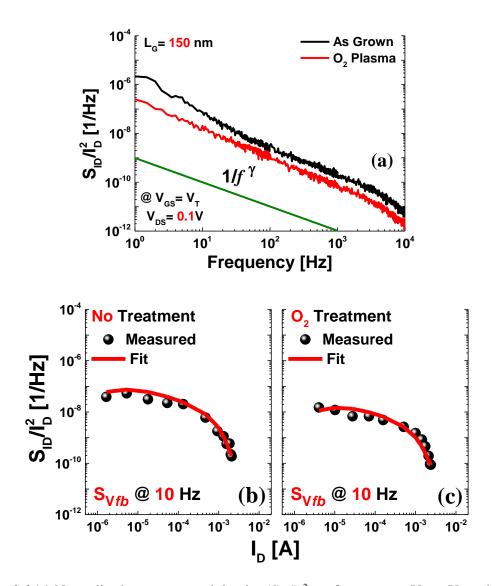

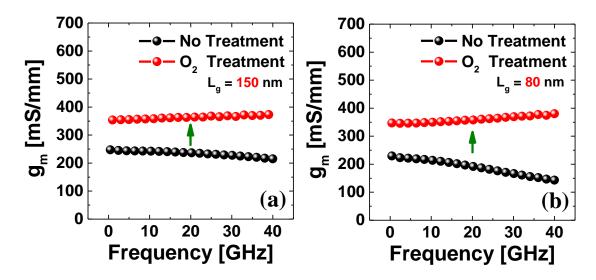

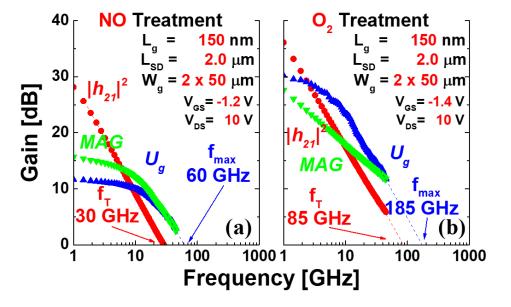

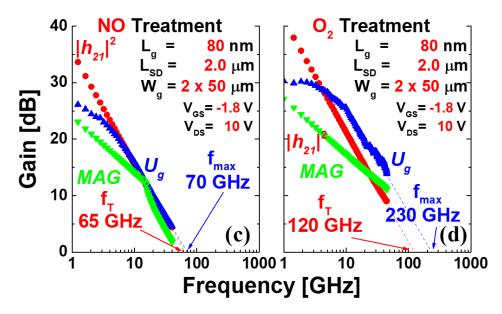

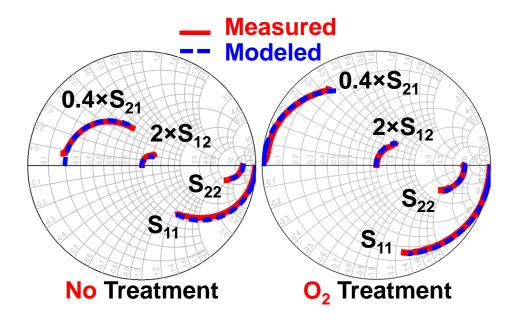

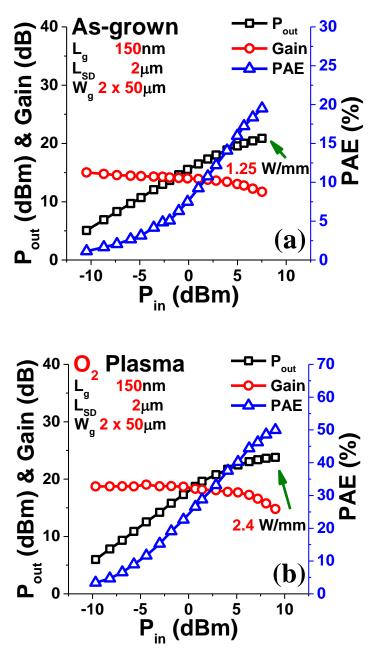

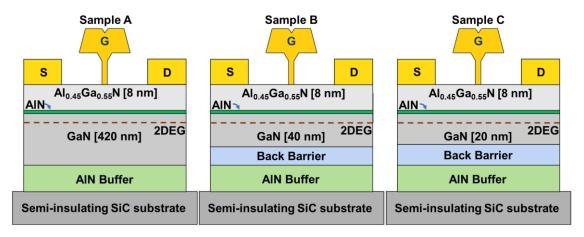

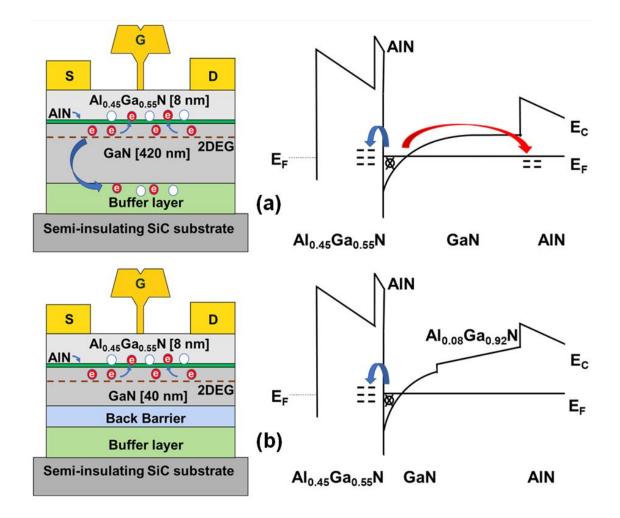

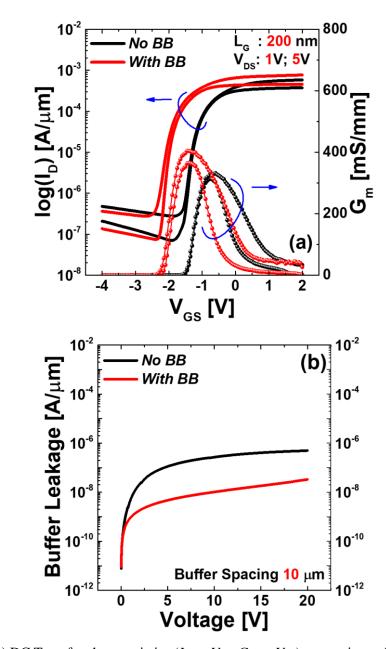

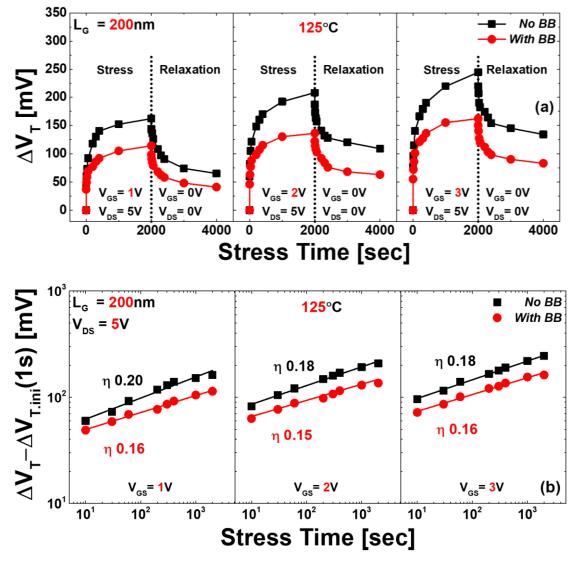

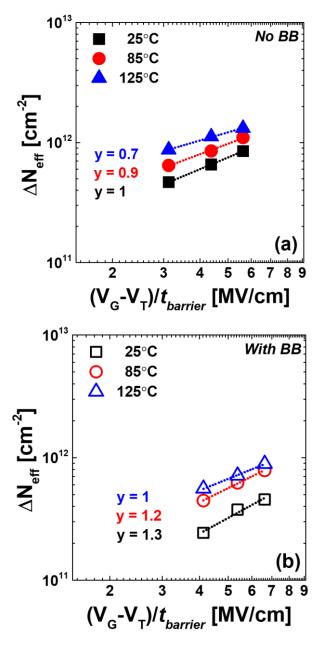

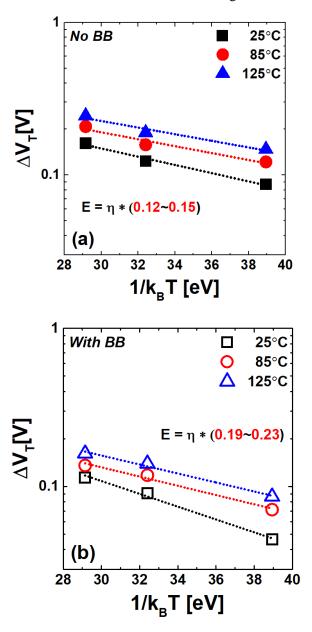

Figure 6-1 Schematic cross-section showing the effects of the O<sub>2</sub> plasma treatment on the 70 bulk of AlGaN barrier layer. Figure 6-2 (a,b) Al 2p and (c,d) Ga 3d core-level spectra of the as-grown and O2 plasma-71 treated samples. Figure 6-3 Comparison of the high-resolution X-ray diffraction (HR-XRD) ( $\omega$ -2 $\theta$ ) 72 profiles of the as-grown and O<sub>2</sub>-plasma treated samples. Figure 6-4 Drain current characteristics under different reverse–sweep drain–stress bias 74 conditions of the (a) as-grown and (b) plasma-treated samples. (c) Leakage Current and (d) Off-state break-down voltage comparison between the samples for  $L_g = 150$  nm devices. Figure 6-5 (a) Single short–pulse  $I_D$ - $V_{GS}$  measurement data. (b) Drain current degradation 75 with respect to time, showing charge trapping. Figure 6-6 (a) Normalized power spectral density  $(S_{ID}/I_D^2)$  vs frequency at  $V_{GS} = V_T$  and 76  $V_{DS} = 0.1V$ . Measured and modelled fitting values of noise spectral density  $(S_{ID}/I_D^2)$  with respect to the drain current  $(I_D)$  at a frequency of 10 Hz: (b) asgrown and (c) plasma-treated samples. Figure 6-7 78 RF  $g_m$  of the samples as a function of the frequency (a)  $L_g = 150$  nm (b)  $L_g =$ 80 nm. Figure 6-8 RF Gains as a function of the frequency at  $V_{DS} = 10V$ , near the peak  $g_m$  gate 78 voltage: (a) as–grown  $L_g = 150$  nm (b)  $O_2$  plasma  $L_g = 150$  nm (c) as–grown  $L_g$ = 80 nm (d)  $O_2 \text{ plasma } L_g = 80 \text{ nm}$ . Figure 6-9 Small-signal modelling analysis for  $L_g = 80$  nm devices at  $V_{GS} = -1.8V$ ;  $V_{DS}$ 80 =10V with measured and modelled data. Figure 6-10 Output power characteristics for  $L_g = 150$  nm devices measured at 8GHz, with 81 a drain bias of  $V_{DS}$  = 25V (a) As-grown (b) O<sub>2</sub> Plasma. Figure 7-1 84 Cross-section schematics of the samples used in this study. Figure 7-2 Schematic cross-section and band diagram showing the effects of "Hot 85 electron" trapping in AlGaN/GaN hemts (a)  $t_{ch} = 420$  nm without back–barrier (b)  $t_{ch} = 40 \text{ nm}$  with back—barrier. (a) DC Transfer characteristics ( $I_D$  vs  $V_{GS}$ ,  $G_m$  vs  $V_{GS}$ ) comparison of the Figure 7-3 86 samples. (b) Buffer leakage current comparison showing the effect of including back-barrier. Figure 7-4 87 (a) Threshold voltage shift  $(\Delta V_T)$  corresponding to stress time showing charge trapping and detrapping phenomena. (b) Power-law time dependency of the samples after removing fast transient charging components ( $V_T$  -  $V_{T.initial}$  (1 s)). Figure 7-5 Effective trap density ( $\Delta N_{eff}$ ) with respect to applied stress electric field 89 showing voltage dependency (y) of (a)  $t_{ch} = 420$  nm without back-barrier (b)  $t_{ch} = 40 \text{ nm with back-barrier.}$

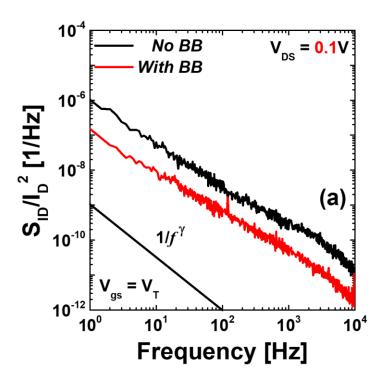

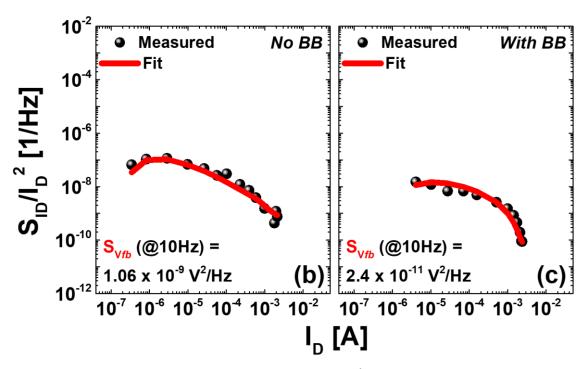

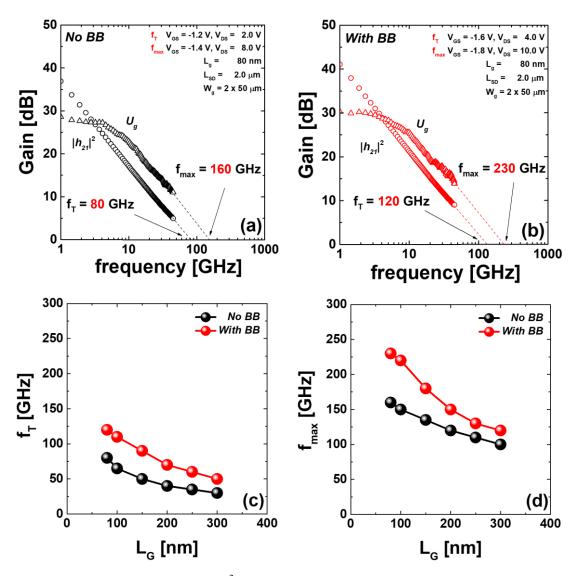

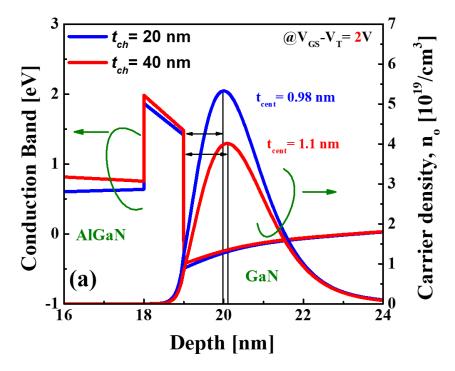

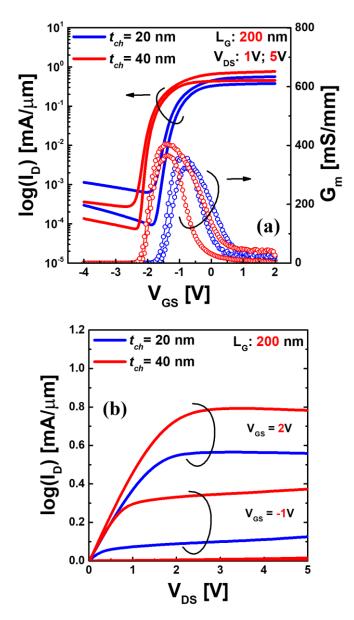

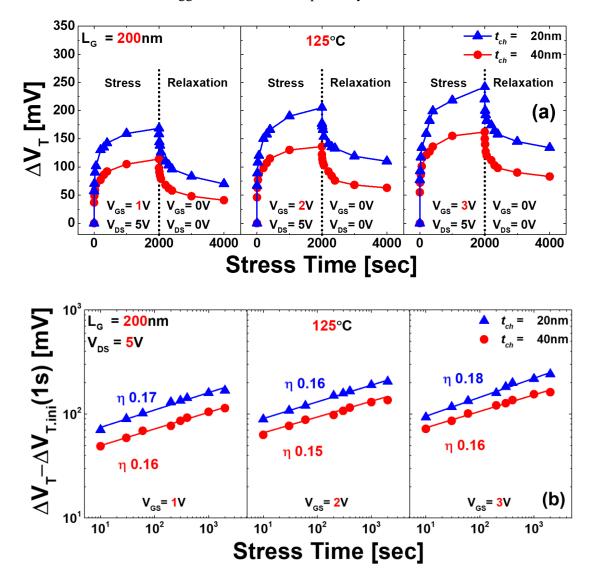

Figure 7-6 Arrhenius plot showing  $\Delta V_T$  activation energy for (a)  $t_{ch} = 420$  nm without 90 back–barrier (b)  $t_{ch} = 40$  nm with back–barrier. Figure 7-7 (a) Drain current power spectral density  $(S_{ID}/I_D^2)$  as a function of frequency at 92  $V_{GS} = V_T$  and  $V_{DS} = 0.1V$ . Measured and modelled  $S_{ID}/I_D^2$  fitting values with respect to the drain current ( $I_D$ ) at a frequency of 10 Hz: (a)  $t_{ch} = 420$  nm without back–barrier (b)  $t_{ch} = 40 \text{ nm}$  with back–barrier. Figure 7-8 Measured RF Gains  $(|h_{21}|^2, U_g)$  as a function of frequency, at near the peak  $g_m$ 93 bias conditions for L<sub>G</sub>= 80 nm devices: (a)  $t_{ch}$  = 420 nm without back–barrier (b)  $t_{ch} = 40$  nm with back–barrier.  $f_T$  and  $f_{max}$  values corresponding to  $L_G$  for (c)  $t_{ch} = 420 \text{ nm}$  without back–barrier (d)  $t_{ch} = 40 \text{ nm}$  with back–barrier. Figure 7-9 94 Band ( $E_c$ ) simulation of the samples with carrier density ( $n_o$ ) profiles. 95 Figure 7-10 (a) DC transfer characteristics (b) Output characteristics. Figure 7-11 (a) Threshold voltage shift ( $\Delta V_T$ ) corresponding to stress time showing charge 96 trapping and detrapping phenomena. (b) Power-law time dependency of the samples after removing fast transient charging components ( $V_T$  -  $V_{T.initial}$  (1 s)). Figure 7-12 (a) Drain current power spectral density  $(S_{ID}/I_D^2)$  as a function of frequency at 97  $V_{GS} = V_T$  and  $V_{DS} = 0.1V$ . Measured and modelled  $S_{ID}/I_D^2$  fitting values with respect to the drain current ( $I_D$ ) at a frequency of 10 Hz: (a)  $t_{ch} = 20$  nm (b)  $t_{ch}$ = 40 nm.Figure 7-13 Measured RF Gains ( $|h_{21}|^2$ ,  $U_g$ ) as a function of frequency, at near the peak  $g_m$ 99 bias conditions for L<sub>G</sub>= 80 nm devices: (a)  $t_{ch}$  = 20 nm (b)  $t_{ch}$  = 40 nm.

# LIST OF TABLES

| Table 2-1 | Comparison of physical properties of various semiconductors for high- |    |

|-----------|-----------------------------------------------------------------------|----|

|           | voltage applications.                                                 |    |

| Table 2-2 | Comparison of JFOM and BFOM for Si, GaAs and GaN materials.           | 19 |

| Table 2-3 | Comparison of substrate properties.                                   | 22 |

| Table 4-1 | Parameters used and extracted values of $D_{it}$ and $N_{bt}$ .       | 50 |

| Table 5-1 | Comparison of Key Reliability Parameters in AlGaN/GaN HEMTs.          | 64 |

| Table 6-1 | Plasma treatment conditions used in this study.                       | 70 |

| Table 6-2 | Comparison of key device parameters for $L_G = 150$ nm.               | 73 |

## Chapter 1

### Introduction

### 1.1 III-V Compound Semiconductor

III-V transistors, particularly those based on compound semiconductors, have a fascinating history and pivotal contributions to the field of electronics. The III-V semiconductor materials consist of elements from groups III and V of the periodic table. The most common compound semiconductors in this category are made from elements like gallium (Ga), indium (In), and aluminum (Al) from group III combined with nitrogen (N), phosphorus (P), arsenic (As), or antimony (Sb) from group V.

The development of III-V compound semiconductors, particularly gallium arsenide (GaAs), played a crucial role in the evolution of transistors[1]. GaAs has exceptional electrical properties that allow for high-frequency operation, making it suitable for radiofrequency applications[2]. In the 1970s and 1980s, GaAs-based transistors gained prominence in the industry, especially for high-frequency and high-power applications, due to their faster switching speed and power handling capabilities compared to silicon-based transistors.

One of the significant advancements was the invention of the high electron mobility transistor (HEMT) in the late 1970s and early 1980s. HEMTs, also known as modulation-doped field-effect transistors (MODFETs), are crucial components in radiofrequency amplifiers, microwave devices, and high-speed integrated circuits[3]. They utilize III-V materials like GaAs and InP (Indium Phosphide) and offer high electron mobility, making them highly suitable for high-frequency and high-speed applications.

Over time, other III-V materials like InP (Indium Phosphide) and GaN (Gallium Nitride) have emerged, contributing to advancements in semiconductor technology[4][5]. Gallium Nitride transistors, in particular, have demonstrated their potential in power electronics, RF amplifiers,

and even in optoelectronic applications like LEDs and laser diodes.

The evolution of III-V semiconductor technology has been a crucial part of the development of compound semiconductor devices. Their capabilities in high-frequency operation, power handling, and efficiency have expanded their use in various applications, including telecommunications, satellite communications, radar systems, and more, and continue to be an area of active research and development.

### 1.2 GaN High Electron Mobility Transistors

Gallium Nitride High Electron Mobility Transistors (GaN HEMTs) represent a critical breakthrough in semiconductor device technology. This class of transistors is built from gallium nitride, a robust wide-bandgap semiconductor material with remarkable electrical properties. GaN HEMTs have garnered significant attention due to their potential for high-power, high-frequency applications. The exceptional characteristics of GaN, with its high band-gap (measuring at 3.4 eV), enable GaN-based devices to endure remarkably high voltages[6]. Demonstrations have shown GaN-based devices with a notably high breakdown voltage reaching 8300 V[7]. Moreover, the III-nitride material's piezoelectric effect and spontaneous polarization facilitate a high sheet carrier density, surpassing 10<sup>13</sup> cm<sup>-2</sup> in AlGaN/GaN heterostructures without the need for conventional doping[8][9]. This attribute translates to easily attainable high current density within GaN HEMTs. The combination of its high voltage handling capability and the capacity for high current density render GaN HEMTs exceedingly suitable for high-power applications.

Furthermore, the significant conduction band discontinuity between AlGaN and GaN results in the AlGaN/GaN structure exhibiting a high electron mobility (exceeding 2000 cm<sup>2</sup>/V-s) and an exceptionally high electron saturation velocity (measured at  $2.5 \times 10^7$  cm/s)[10][6]. These features pave the way for high-frequency and high-power operations, highlighted by the demonstration of an  $f_T$  (Unity current gain cutoff frequency) of 454 GHz and  $f_{max}$  (Maximum oscillation frequency) of 554 GHz using a 20 nm 'T' gate device with a 100% Al in the AlGaN barrier and n<sup>+</sup> GaN source/drain contact[6]. The unique material properties of GaN bestow AlGaN/GaN HEMTs with exceptional performance across a wide range of frequencies in RF power applications. Impressively, demonstrations have showcased an output power density of 40

**Figure 1-1** (a) A technology roadmap for RF GaN HEMTs. (b) A technology roadmap for Power GaN HEMTs.[11]

W/mm at 4 GHz, 13.7 W/mm at 30 GHz, and 2.1 W/mm at 80.5 GHz, eclipsing the capabilities of conventional technologies reliant on GaAs or InP[12][13][14]. GaN HEMTs exhibit unparalleled performance, offering substantial promise for applications demanding high-power, high-frequency functionality, such as WLAN base stations and high-voltage switching applications in power electronics. The roadmap in GaN HEMTs applications is illustrated in figure 1-1.

### 1.3 Motivation

A major challenge currently constraining the widespread adoption of GaN HEMT technology is its constrained device performance due to electrical reliability. Despite notable advancements in the reliability of GaN HEMTs in recent years, these devices continue to contend with various degradation mechanisms[15][16]. Consequently, GaN HEMTs have not yet achieved robust reliability in both RF and DC applications. For instance, figure 1-2 shows the drain current degradation observed in AlGaN/GaN HEMT devices during pulsed I-V measurement, an experiment conducted within this study. The measurement involved applying a single short pulse in the gate, recording  $V_G$  pulse and its corresponding  $I_D$  response, which were then transformed into  $I_D$ – $V_{GS}$  or  $I_D$ –time curves. Notably, hysteresis and drain current degradation over time due to charge trapping within the AlGaN barrier were observed. These trapping phenomena lead to a decline in device performance, posing a significant challenge, particularly for applications such as satellite communications, which demand exceptionally high reliability. Given that these devices are designed for high-frequency, high-power, and high-voltage applications and are expected to operate at high temperatures due to GaN's high band-gap, ensuring solid device performance becomes particularly challenging in extreme operating environments without robust reliability.

**Figure 1-2** Pulsed  $I_D$  vs  $V_{GS}$  and  $I_D$  vs. pulse time showing  $\Delta I_D$  degradation due to charge trapping.

In order to achieve consistent device performance with robust reliability, it requires a comprehensive understanding of the underlying physical mechanisms behind device degradation. This involves understanding how normal or stressed operational conditions—such as current, voltage, temperature, and environmental factors—contribute to degradation. It is vital to identify which device performance parameters ( $I_D$ ,  $G_m$ ,  $V_T$ ) degrade, the process of degradation, and the influence of device design, encompassing device geometry and heterostructure. Furthermore, as there's typically a trade-off between performance and reliability, a comprehensive grasp of the degradation's physics allows for the strategic design of device structure and heterostructure to achieve an optimized balance between performance and reliability. Additionally, understanding the physical degradation mechanism is critical for assessing device reliability. Defect sites within the epitaxial layers stand as the primary reason behind the degradation of GaN HEMTs, actively capturing and emitting channel electrons during device operation. These trapping phenomena intensify under stressed conditions, typically evaluated to determine device reliability. A profound comprehension of the physical mechanisms behind charge trapping is pivotal for enabling the proper scalability of GaN HEMTs, and facilitating performance enhancement.

To date, numerous hypotheses have emerged to elucidate the degradation of GaN HEMTs. Prominent among these theories are hot-electron-induced trap formation, hot electron trapping at the surface, and the development of crystallographic defects via the inverse piezoelectric effect[15][16][17]. However, our comprehension of device degradation remains incomplete, necessitating a more intricate understanding of these mechanisms and the discovery of potential yet-unidentified degradation pathways. Moreover, the development of novel measurement techniques tailored to investigate diverse phenomena within GaN HEMTs is imperative for achieving a deeper insight into these degradation mechanisms.

In this thesis, we delve into the intricate physical mechanisms underlying the degradation of AlGaN/GaN HEMTs by employing an array of device characterization techniques. Our objective is to shed light on pathways for enhancing device scalability while concurrently improving device reliability.

### 1.4 Objectives

This thesis encompasses a comprehensive investigation into the physical mechanisms of trapping-related degradation in AlGaN/GaN high electron mobility transistors (HEMTs), seeking to advance device reliability and performance.

- 1. The primary objective revolves around scrutinizing the impact of trapping effects on device performance, understanding trapping mechanisms within the AlGaN barrier and AlGaN/GaN interface as well as the impact of Al composition in the AlGaN barrier.

- 2. Secondly, evaluating the influence of various structural modifications on these devices. Exploring the impact of O<sub>2</sub> plasma treatment on the surface as well as the volume trap states within the AlGaN barrier layer, focusing on the scaling down of channel thickness, the impact of the Al<sub>0.08</sub>Ga<sub>0.92</sub>N channel back barrier.

These objectives have been approached through a multi-faceted reliability analysis, incorporating frequency-dependent *C-V* and *G-V* methods, pulsed *I-V* characterizations, low-frequency 1/f noise characterizations, and Positive-Bias-Temperature Instability (PBTI). The intent is to establish a deeper understanding of these trapping mechanisms, and their impact on device reliability and scalability, and to propose measures to enhance device performance without compromising reliability. The work aims to contribute insights and strategies that can propel the advancement of AlGaN/GaN HEMTs in high-power, high-frequency applications while ensuring their long-term reliability and robust performance.

### 1.5 Thesis outline

The thesis is structured as follows: Chapter 2 presents background information on GaN-based HEMTs, discussing key technologies and reliability issues related to high-performance GaN HEMTs.

Chapter 3 offers an overview of the AlGaN/GaN HEMTs utilized in this study, delving into the fabrication process and detailing the chip designed specifically for this research. Additionally, the chapter comprehensively explains the various reliability characterization methods employed throughout the study. These methods encompass interface and border trap characterization,

volume trap density extraction, low-frequency noise characterizations, the pulsed *I-V* technique, and the methodology for stress characterizations.

Chapter 4 provides an in-depth overview of the extraction of interfacial trap densities in AlGaN/GaN HEMTs. It reports, for the first time, the use of conventional frequency-dependent C-V and G-V methods to characterize the interface trap density ( $D_{ii}$ ) between AlGaN and GaN and the deep-level/border trap density ( $N_{bi}$ ) in the AlGaN barrier layer in a long-channel AlGaN/GaN HEMT fabricated on a SiC substrate. The primary focus was on the trap states inside the AlGaN layer, situated at the interface and near the interface of the AlGaN/GaN, with attempts made to eliminate other potential interfacial trap-contributing factors, such as dielectric layers for passivation.

In Chapter 5, an in-depth trapping characteristic analysis of the Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN interface of AlGaN/GaN HEMTs based on the variation of Al composition in the Al<sub>x</sub>Ga<sub>1-x</sub>N barrier and its effects on device performance was presented. It demonstrates that trapping effects, significantly impacting device performance, are primarily influenced by the quality of the interface between the AlGaN and GaN layers.

Chapter 6 analyzes in detail the effect of employing O<sub>2</sub> plasma treatment before the deposition of the gate metal on top of an AlGaN layer. It demonstrates that the O<sub>2</sub> ions not only passivated the AlGaN gate surface area but also penetrated into the bulk, forming Al–O and Ga–O bonds, while treating the volume trap states. Additionally, RF gm collapse effects were improved, ultimately increasing the microwave output performance.

Chapter 7 introduces structural modifications, such as the inclusion of an AlGaN channel back barrier and channel thickness scaling to improve device performance. Positive Bias Temperature Instability (PBTI) and its correlation with trapping effects, responsible for device instabilities, are extensively explored. These modifications are demonstrated to significantly improve  $f_T$  and  $f_{max}$  of the devices.

Finally, Chapter 8 concludes by summarizing the research findings and proposing guidelines for enhancing reliability in device design. Additionally, it provides recommendations for future research.

# **Chapter 2**

### **Fundamentals of GaN HEMTs**

### 2.1 GaN material properties

Gallium Nitride (GaN), a wide-bandgap semiconductor, has garnered considerable attention in the field of electronics due to its unique material properties that make it exceptionally well-suited for high-power, high-frequency applications. This semiconductor's distinct characteristics set it apart from others and position it as a key material for the next generation of electronic devices.

One of the standout features of GaN is its wide energy gap, measuring approximately 3.4 eV[18]. This energy gap is more than three times that of silicon (Si). The significance of this wide energy gap lies in its ability to withstand high electric fields. GaN exhibits a high breakdown electric field of 3.3 MV/cm, making it a robust choice for high-power and high-frequency applications that often require operation at elevated temperatures[6]. As a result, GaN has found extensive use in both commercial and military markets.

GaN's remarkable electron mobility, which measures approximately 900 cm<sup>2</sup>/V·s, is another defining property. This high electron mobility, combined with GaN's capacity to handle high voltages, allows for higher saturation velocities, reaching up to 2.7 x 10<sup>7</sup> cm/s[18]. These properties are instrumental in enhancing operating frequencies, making GaN-based devices well-suited for high-frequency applications.

In addition to its electronic properties, GaN also exhibits excellent mechanical and thermal stability. This, along with its good thermal conductivity, makes GaN an ideal choice for dissipating heat. Devices fabricated on silicon carbide (SiC) substrates, using GaN, can operate at higher temperatures and power levels, which is crucial for many applications. Comparing the key material properties of GaN with other well-known semiconductors, such as silicon (Si), highlights GaN's unique advantages. Here is a table that compares the basic material properties

of GaN with other well-known semiconductors:

**Table 2-1** Comparison of physical properties of various semiconductors for high-voltage applications[18].

| Material Properties                                      | Si            | 6H-SiC      | GaAs         | GaN           |

|----------------------------------------------------------|---------------|-------------|--------------|---------------|

| Bandgap Energy (eV)                                      | 1.1           | 3.0         | 1.43         | 3.4           |

| Electron Mobility (cm²/V·s)                              | 1400          | 400         | 8500         | 900           |

| Saturated (Peak) Drift Velocity (x 10 <sup>7</sup> cm/s) | 1.0           | 2.0         | 2.1          | 2.7           |

| Breakdown Electric Field (MV/cm)                         | 0.3           | 2.4         | 0.4          | 3.3           |

| Thermal Conductivity (W/cm·K)                            | 1.5           | 4.5         | 0.5          | 1.3           |

| Relative Dielectric Constant                             | 11.8 (static) | 9.7<br>(HF) | 6.7 (static) | 12.9 (static) |

These properties collectively highlight GaN as a standout material for high-power, high-frequency applications. Its wide energy gap, high electron mobility, and excellent thermal characteristics contribute to its superior performance.

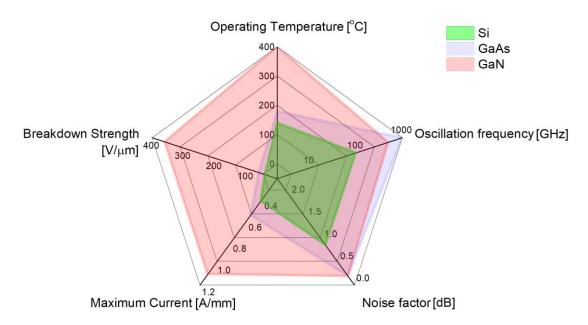

Figure 2.1 provides a comparison among GaN, Si, and GaAs, highlighting their respective advantages in RF and power supply circuits. It illustrates that GaN stands out as the primary material for the upcoming generation of high-frequency, high-power, high-voltage, high-temperature, and low-loss operating specification transistors[18]. Hence, GaN is deemed an excellent and prominent candidate for high-performance HEMTs.

GaN's potential as a high-performance semiconductor is further reinforced by two key figures of merit:

- Johnson's Figure of Merit (JFOM) assesses a device's ability to operate at both high power and high frequency. It is calculated as the product of electric field breakdown ( $E_C$ ) and electron saturation velocity ( $V_S$ ). Higher JFOM values indicate a device's enhanced capability to handle high power and high-frequency operation[19].

$$JFOM = \frac{E_C V_S}{2\pi} \tag{2.1}$$

- Baliga's Figure of Merit (BFOM) gauges the resistive losses of a device and is vital for evaluating the performance of power electronic devices. It is determined by factors such as the dielectric constant ( $\varepsilon$ ), carrier mobility ( $\mu$ ), and the critical breakdown field ( $E_C$ ) of the semiconductor[20].

$$BFOM = \in \mu E_C^3 \tag{2.2}$$

When comparing these figures of merit, GaN outperforms traditional semiconductors by a significant margin.

Figure 2-1 Comparison of GaN material merits to Si and GaAs.

Table 1.2 presents a comparison between GaN and conventional semiconductor materials. The figures of merit are normalized concerning those calculated for silicon (Si) material. Higher values indicate greater desirability. The comparison outlines the Johnson Figure of Merit (JFOM) and Baliga Figure of Merit (BFOM) for Si, GaAs, and GaN materials[21]:

Table 2-2 Comparison of JFOM and BFOM for Si, GaAs and GaN materials[21].

| Material | JFOM/JFOM (Si) | BFOM/BFOM (Si) |

|----------|----------------|----------------|

| Si       | 1              | 1              |

| GaAs     | 1.8            | 14.8           |

| GaN      | 215.1          | 186.7          |

In summary, GaN's wide energy gap, high electron mobility, high saturation velocity, and excellent thermal properties make it an ideal candidate for high-performance HEMTs and other electronic devices. Its figures of merit demonstrate that GaN surpasses traditional semiconductors, positioning it as a key material for the next generation of high-frequency, high-power, high-voltage, high-temperature, and low-loss electronic devices.

### 2.2 AlGaN/GaN High Electron Mobility Transistors

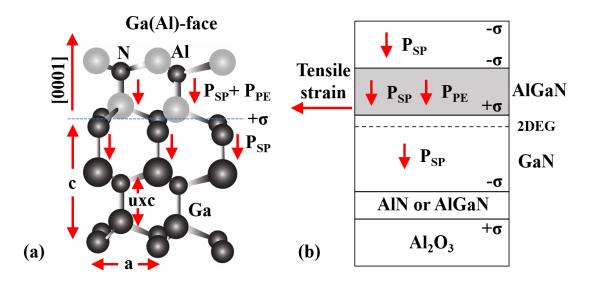

AlGaN/GaN HEMT epitaxy techniques encompass molecular beam epitaxy (MBE) and metal-organic chemical vapor deposition (MOCVD)[22][23]. While MBE-grown devices showcase a performance comparable to those produced through MOCVD[24], the long-term cost efficiency favors MOCVD over MBE for commercial AlGaN/GaN HEMT growth. Both AlN and GaN exhibit a wurtzite-type hexagonal crystal structure[25]. GaN epitaxy comes in two forms based on the cut-face: Ga-polar and N-polar. Typically, Ga-polar film is grown using MOCVD, while N-polar film is cultivated by MBE under specific conditions[26]. The devices analyzed in this study are Ga-polar AlGaN/GaN HEMTs. Due to the higher electronegativity of nitrogen compared to gallium and aluminum, GaN and AlN demonstrate strong spontaneous polarization, measuring 0.029 and 0.081 C/m², respectively[27]. Additionally, these materials exhibit piezoelectric polarization as piezoelectric substances. When a thin layer of Al<sub>x</sub>Ga<sub>1-x</sub>N is grown atop Ga-polar GaN, it undergoes tensile strain, resulting in piezoelectric polarization aligned with the spontaneous polarization (Figure 2-2 b). This substantial polarization generates an electric field within the AlGaN layer.

**Figure 2-2** (a) the Ga-polar GaN crystal structure and (b) the presence of spontaneous and piezoelectric polarization within the Ga-polar system, featuring the 2DEG situated at the lower AlGaN/GaN interface[28].

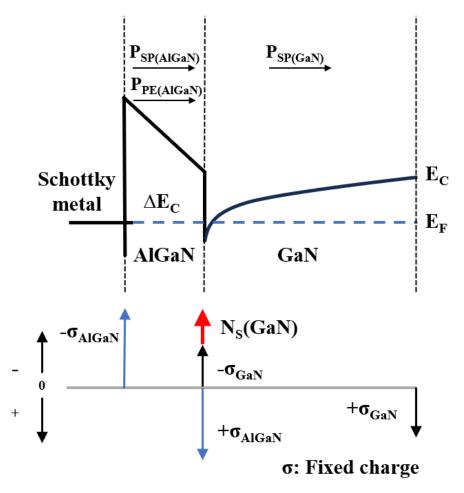

In unintentionally doped AlGaN, it is assumed that surface donor states exist at the top of the AlGaN layer. When the AlGaN layer reaches a sufficient thickness for the Fermi level to access these states, electrons are stimulated to transition into the conduction band. Guided by the electric field, these electrons move towards the AlGaN/GaN interface. Upon reaching the GaN layer, these electrons flow into the GaN side due to its lower Fermi level. This flow continues until the Fermi level equalizes, establishing a 2-dimensional electron gas (2DEG) at the AlGaN/GaN interface[29]. These electrons are confined at the interface, as illustrated in Figure 2-3, yet exhibit high mobility within the AlGaN/GaN interface. Tuning the Al molar fraction x and the thickness of Al<sub>x</sub>Ga<sub>1-x</sub>N can further boost the carrier sheet density and mobility in the 2DEG. An increase in the Al molar fraction and Al<sub>x</sub>Ga<sub>1-x</sub>N thickness augments the carrier sheet density by elevating the piezoelectric polarization. However, this elevation often results in decreased carrier mobility due to increased scattering when the carrier density rises[30].

**Figure 2-3** The energy band diagram and charge distribution illustration of a Ga-polar AlGaN/GaN HEMT in its unbiased state[31].

### 2.3 Substrates

Due to the high cost of GaN substrates, AlGaN/GaN HEMTs are commonly cultivated on alternative substrates such as sapphire, SiC, and Si. Each substrate's properties concerning GaN epitaxy are detailed in Table 2-3. Among these substrates, SiC exhibits the most favorable compatibility with AlGaN/GaN epitaxy, albeit being the most expensive. The more cost-effective alternatives include sapphire or Si, with Si displaying more promising characteristics compared to sapphire. Si substrates are available in larger sizes of up to 12 inches and experience fewer issues with wafer-bow management compared to sapphire[32]. AlGaN/GaN epitaxy is predominantly grown on (111) Si due to its trigonal symmetry, facilitating the epitaxial growth of (0001) GaN[33]. Moreover, growing AlGaN/GaN on Si enables seamless integration between AlGaN/GaN HEMT and Si-based semiconductors[34][35][36]. This integration fosters cost-

effective large-scale production and paves the way for innovative applications. Despite these prospects, there remain numerous reliability issues that demand attention[17]. Consequently, this project endeavors to advance the understanding of the reliability of AlGaN/GaN HEMT-on-Si.

**Table 2-3** Comparison of substrate properties

| Properties                                                                | Sapphire | SiC       | Si    | GaN            |

|---------------------------------------------------------------------------|----------|-----------|-------|----------------|

| Lattice mismatch (%)                                                      | 16       | 3.1       | -17   | 0              |

| Linear thermal expansion coefficient (×10 <sup>-6</sup> K <sup>-1</sup> ) | 7.5      | 4.4       | 2.6   | 5.6            |

| Thermal conductivity (W cm <sup>-1</sup> K <sup>-1</sup> )                | 0.25     | 4.9       | 1.6   | 2.3            |

| Cost                                                                      | Cheap    | Expensive | Cheap | Very Expensive |

| Dislocation density of GaN film (cm <sup>-2</sup> )                       | $10^{8}$ | $10^{8}$  | 109   | 104-106        |

### 2.4 Failure Mechanism

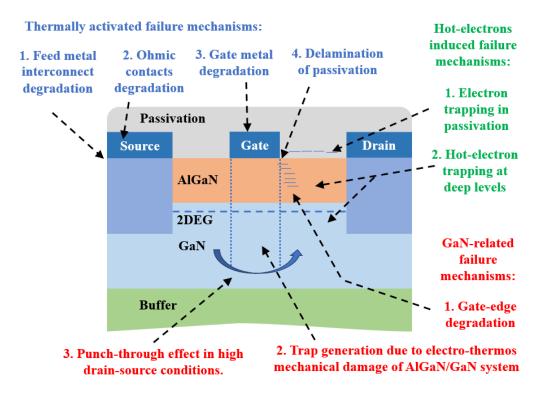

GaN HEMTs present distinctive reliability challenges associated with material properties and the quality of epitaxial growth[37][38][15][39]. In Figure 2-4, a schematic cross-section of an AlGaN/GaN HEMT is depicted, outlining primary failure mechanisms reported in the literature. These are briefly summarized below. The primary objective is to spotlight some of the most recent findings that are pertinent to state-of-the-art devices and future advancements.

**Figure 2-4** Illustrative diagram depicting the primary mechanisms influencing the reliability of GaN-based High Electron Mobility Transistors (HEMTs)[16].

### 2.4.1 Inverse Piezoelectric Effect and Thermo-mechanical Strain

The most sensitive region in a GaN HEMT is situated in the semiconductor layers near the gate's drain-side edge, where high current density, electric field, and localized temperature coincide. At this specific location, various degradation mechanisms are expedited: the piezoelectric properties of GaN lead to amplified tensile stress within the AlGaN barrier due to the presence of an electric field. This stress relief often generates lattice defects or cracks, resulting in the decline of drain current ( $I_D$ ) and an upsurge in gate leakage current ( $I_G$ ). Even without applied bias, thermal cycling at elevated temperatures (300–650K) can prompt crack formation owing to thermal mismatches among GaN, gate metallization, and  $Si_xN_\gamma$  passivation. The thermo-mechanical strain concentrates primarily at the gate edges, symmetrically impacting the gate center, leading to structural damage on both the source and drain sides [40][41].

### 2.4.2 Time-Dependent Breakdown of the AlGaN/GaN Structure and Dielectrics

The polar nature of chemical bonds in GaN can instigate defect formation under the influence of a strong electric field, leading to the organization of these defects into a conductive percolative pathway. This results in a sudden increase in  $I_G$ . The degradation kinetics align with a time-dependent dielectric breakdown (TDDB) mechanism: during a gate state at a constant voltage in the off-state, the gate current initially becomes erratic, followed by a sudden surge of several orders of magnitude[42][43][44][45]. Conductive pathways manifest on the device's surface at the gate edge and can be detected using electroluminescence (EL) microscopy[45]. Direct observation of the damaged region, typically extending a few nanometers, demands meticulous sample preparation and transmission electron microscopy (TEM). If the leakage is due to a percolative chain of point defects, which are undetectable by TEM, the observation may be elusive. These time-dependent breakdown effects are characteristic of polar semiconductors like GaN and have also been witnessed in InGaN/GaN light-emitting diodes subjected to reverse bias tests[46].

The high electric field within the device places dielectrics under significant stress, making them susceptible to TDDB mechanisms. Notably, a critical point is the dielectric below the gate field-plate edge[47][48].

### 2.4.3 Electro-chemical GaN Oxidation

Under the influence of elevated temperatures and high electric fields, gate metals and contaminants can diffuse toward the semiconductor surface, particularly at the sidewall interface between the metal and passivation (typically  $Si_xN_y$ ). Interdiffusion involving elements like Au, O, and others has been observed[49][50]. Under specific conditions (such as the presence of moisture, high temperatures, high electric fields, and device current), oxygen may react with GaN at the device surface, leading to the formation of pits and voids near gate edges. This can result in an increase in the parasitic resistance of access regions and a decrease in transconductance. Electrochemical dissolution of GaN can progressively damage the structure at the gate's drain edge, leading to the formation of pits and grooves associated with the presence of oxygen or water vapor, resulting in the formation of Ga and Al oxide[51].

A rather complex chain of electrochemical reactions, necessitating the presence of holes

generated by band-to-band tunneling, has been recognized as a potential mechanism for GaN surface oxidation. Additionally, other researchers observed the formation of an interfacial layer under the gate contact, comprising an amorphous layer of aluminum oxide formed from the expulsion of nitrogen and the consumption of aluminum from an as-formed interfacial layer composed of Al, Ga, O, and N[52]. Schottky and ohmic contacts on GaN and related compounds generally demonstrate stability at high temperatures[53]. Both Schottky and ohmic contacts can endure temperatures of up to 300°C for extended periods, although Ni has been reported to form NiO and Ni-nitrides starting at annealing temperatures as low as 200°C.

### 2.4.4 Hot Electron Effects

Enduring and reversible trapping and detrapping effects can induce substantial device drift, leading to alterations in threshold voltage and transconductance. These effects might stem from material quality, such as pre-existing deep levels on the surface, at interfaces, within the GaN buffer, or the semi-insulating substrate, or they may arise from process-induced instabilities, particularly concerning compensating species (Fe or C), contaminants like H, F, O, or defects [54]. Hot-electron effects, resulting in the generation of deep levels and electron trapping in dielectrics, surfaces, and interfaces under the gate, particularly in the gate-drain access region, may occur during off-state tests or, more frequently, during semi-on and on-state tests [55].

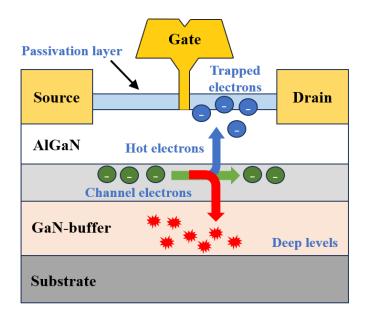

The term "hot electrons" refers to non-equilibrium electrons with sufficient kinetic energy to surpass potential energy barriers, being injected into buffer, barrier, or insulating layers, where they become trapped, break atomic bonds, and create interface states or activate traps, for instance, via dehydrogenation, as illustrated in Figure 2-6 [56][57][58]. Depending on experimental conditions, material properties, and device weaknesses, hot electrons may lead to parametric, gradual, permanent, or recoverable positive or negative threshold voltage shifts, and/or a reduction in transconductance.

**Figure 2-5** Schematic cross-section of an AlGaN/GaN HEMT illustrating potential consequences of hot electrons: these electrons have the potential to be captured at interfaces, within the GaN buffer, on the surface, or within passivation layers [59].

In Si n-MOSFET, holes generated by impact ionization can be collected as substrate current Ib; in AlGaAs/GaAs HEMTs, impact ionization hole current induces a negative gate current Ig, which can be associated with hot-electron effects[60]. Due to the different leakage mechanisms in a GaN HEMT and the reduction of impact ionization effects because of the wide bandgap, the gate current is not indicative of hot-electron phenomena, unless the devices being studied exhibit extremely low leakage current[61].

Characterizing hot-electron effects in GaN HEMTs typically relies on the measurement of electroluminescence (EL), owing to intraband transitions of energetic electrons (Bremsstrahlung)[62]. EL exhibits a non-monotonic behavior concerning gate voltage: starting from pinch-off and increasing gate-source voltage ( $V_{GS}$ ), EL initially increases as 2DEG density in the channel is elevated. At high  $V_{GS}$ , as gm saturates, EL decreases due to the electric field decrease with increasing  $V_{GS}$ . This characteristic can be utilized to verify if the failure mechanism is due to hot electrons by examining if, at a given drain-source voltage ( $V_{DS}$ ), the degradation shows the same non-monotonic dependence on  $V_{GS}$  as EL.

### 2.4.5 Trapping Phenomena

GaN HEMTs are known to exhibit significant trapping effects[63]. It is commonly believed that, under high voltage, surface states between the gate and the drain trap electrons that tunnel from the gate metal[64][65][66]. Additionally, hot electrons from the channel can be trapped at the surface[67]. The accumulation of these trapped electrons at the surface or within the AlGaN barrier alters the electrostatics, depleting channel carriers in the extrinsic drain, and consequently reducing the drain current[64]. In a study by Koley et al., the surface potential in the extrinsic region was measured using the Kelvin probe technique, revealing the accumulation of a negative charge on the surface when subjected to high voltage[65]. It was postulated that the trapped electrons originated from the gate and were not hot electrons from the channel, as no current flowed in the channel during their high-voltage experiment.

Although trapping at the surface or within the AlGaN barrier layer is thought to be predominant, it is also suggested that electron trapping in the GaN buffer may occur, leading to degraded device performance. Trapping in GaN HEMTs generally displays a slow nature, with a recovery time from current collapse often being long (>100 s or even a few days)[68][64][65]. This indicates that the process of detrapping trapped electrons is typically very slow. Si<sub>x</sub>N<sub>y</sub> passivation is known to alleviate various trapping-related issues[69][70][65] by reducing trap density through the passivation of surface states and by rendering these surface states inaccessible to electrons tunneling from the gate[64]. However, the detailed mechanism of how surface passivation diminishes trapping effects remains unclear.

Efforts have been made to create dispersion-free devices using a specific cap structure[71], and sometimes even without passivation[72]. However, in most instances, surface passivation is considered crucial to alleviate trapping effects and enhance device reliability.

### 2.4.6 Reliability

Numerous researchers have extensively investigated the electrical degradation of GaN HEMTs, a notable challenge observed in GaN HEMT power applications. This degradation is evident in the reduction of drain current, transconductance, output power,  $f_T$ , and  $f_{max}$ , which has been consistently noted in various stress experiments[17][73][74]. While attempts have been made in a few studies to decipher the origins of RF output power degradation[74][75], the

prevalent approach has involved conducting DC stress tests to identify the physical degradation mechanisms.

The decrease in drain current often corresponds to an increase in drain resistance, with source resistance relatively unaffected by electrical stress[68][73]. Moreover, there is observable transconductance degradation[17][55]. Some instances have indicated a positive shift in the threshold voltage[76][73], but a unified understanding regarding the alterations in the device's threshold voltage remains elusive.

After electrical stress, increased trapping behavior has been noted in several instances[68][76]. Although reduced drain current might partially recover, it promptly reverts to its degraded state when stress resumes, signifying evidence of trap creation during stress[68]. Furthermore, gate current degradation has been reported post high voltage stress tests[73], often leading to an extensive increase in reverse gate leakage due to Schottky gate degradation. Recovery in this degradation was not observed. A significant increase in gate current can compromise RF performance, affecting parameters like PAE and gain[77].

Although Schottky characteristics can deteriorate under high voltage stress, they generally remain stable during thermal stress[77][55]. Unlike GaAs devices where gate sinking is a significant degradation mechanism, gate sinking hasn't been reported in GaN HEMTs[15][78]. Notably, apparent ohmic contact degradation hasn't been observed even after extended thermal stress[55][78] or device degradation in high voltage stress tests[79][80].

Studies have primarily focused on mechanisms affecting devices over relatively short periods since GaN HEMTs typically exhibit degradation within a few hours of high-voltage and high-temperature operation. Industry groups have reported diverse DC and RF life test results[77], yet the predicted mean time to failure (MTTF) at 300°C junction temperature varies around 150 hours. The activation energy of the MTTF typically falls between 1.05 and 2 eV, though Coffie et al. have reported a negative activation energy of -0.15 eV[81].

### 2.5 Summary

This chapter discusses the foundational aspects of GaN HEMTs and reviews previous studies concerning GaN failure mechanisms and reliability. It summarizes significant findings on the degradation observed in GaN HEMTs. Our thesis specifically concentrates on two key degradation mechanisms: hot electron effects and material defect-related trapping. We direct our attention toward minimizing these degradation mechanisms by implementing structural modifications aimed at enhancing device performance.

# Chapter 3

## **Experimental setup**

### 3.1 Introduction

This chapter provides an overview of the AlGaN/GaN HEMTs utilized in this study. It delves into the fabrication process and the details of the chip designed specifically for this research. Additionally, the chapter comprehensively explains the various reliability characterization methods employed throughout the study. These methods encompass interface and border trap characterization, volume trap density extraction, low-frequency noise characterizations, the pulsed *I-V* technique, and the methodology for stress characterizations.

### 3.2 Devices and fabrication processes

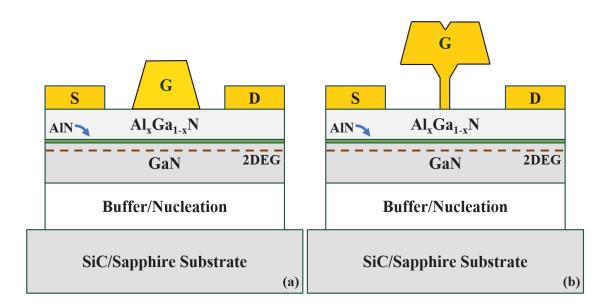

Throughout this study, we utilized various AlGaN/GaN HEMT structures to investigate and enhance the reliability of these devices. In Figure 3-1, you can observe the general cross-section schematics of the AlGaN/GaN HEMTs employed in our research. The wafers used in this study were generously provided by our industrial project collaborators, NTT and KANC. The epitaxial layers were grown on semi-insulating SiC/Sapphire substrates through the metal—organic-chemical-vapor-deposition (MOCVD) method. The layers were deposited in the following sequence, starting from the bottom: an AlN nucleation layer, a high-resistance GaN (or AlN) buffer layer, a GaN channel, an AlN spacer, and an Al<sub>x</sub>Ga<sub>1-x</sub>N barrier layer. The typical thickness of the AlGaN layer ranged from 8 to 28 nm, with an Al composition between 25% and 45%. It's worth noting that these values exhibited slight variations from one

**Figure 3-1** Cross-section schematic of (a) Optical Trapezoidal-shaped gate. (b) EBL "T" shaped gate.

wafer to another. Hall measurements were conducted to determine the mobility  $(\mu_{n\_Hall})$  and the sheet charge density (2DEG), yielding values ranging from 2100 to 2200 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup> and 8 to 9  $\times 10^{12}$  cm<sup>-2</sup>, respectively. Mesa isolation was achieved using Cl<sub>2</sub>-based inductive coupled plasma (ICP) etching to isolate the individual devices. Prior to the deposition of ohmic metal, the substrates underwent a treatment involving a mixture of HCl and deionized water (1:5) for 30 seconds to eliminate any native oxide formation. To facilitate ohmic contact formation, we deposited a Ti/Al/Ni/Au (25/160/40/100 nm) alloy on the source and drain areas using an electron beam (e-beam) evaporator. Subsequently, we performed rapid thermal annealing at 830 °C in an  $N_2$  ambient for 30 seconds. To determine the contact resistance  $(R_C)$  and sheet resistance  $(R_{SH})$ , we employed transmission line-method (TLM) measurements, which yielded values in the range of 0.28 to 0.5  $\Omega$ ·mm and 320 to 550  $\Omega/\Box$ , respectively. We also deposited a Ti/Au (20/300 nm) padding layer using the e-beam evaporator to ensure robust probe contact. Finally, we deposited the gate metal, consisting of Ni/Au (20/400 nm), using the e-beam evaporator. Our research featured two types of gates: trapezoidal-shaped gate "FATFET" devices (Figure 3-1a) and "T" shaped devices (Figure 3-1b). FATFET devices had larger gate lengths ranging from 10 to 50 um, whereas "T" shaped gate devices featured thinner channel gate lengths between 0.016 and 0.5 µm. The standard devices chosen for frequency-dependent trap analysis were the FATFET devices, whereas the majority of our reliability experiments involved devices with gate lengths of less than 0.2 µm. These standard devices had a gate width of 50 µm, and the gate-to-drain and gate-to-source spacing was in the range of 1 to 4  $\mu$ m, with the gate centered in between. A typical device with a gate width of 2 x 50  $\mu$ m achieved a maximum current-gain cut-off frequency ( $f_{T}$ ) of around 120 GHz and a maximum oscillation frequency ( $f_{max}$ ) of approximately 250 GHz.

To systematically investigate reliability, we developed a dedicated reliability test chip, as illustrated in Figure 3-2. Each chip encompasses an area of approximately 63 mm<sup>2</sup> and accommodates a substantial number of the standard devices detailed previously. Most of these devices are fully processed before the via integration stage. They are arranged in close proximity, facilitating equitable comparisons during various stress experiments involving multiple devices. In addition to the standard devices, the chip also incorporates other HEMTs with distinct geometries:

- Gate fingers: 1x, 2x.

- Gate width: 5 μm, 10 μm, 20 μm, 50 μm, 2x5 μm, 2x25 μm, and 2x50 μm.

- Gate to drain distance: 1, 1.5, 2, 2.5, 4 and 6 μm.

- Source to gate distance: 1, 1.5, 2, 2.5, 4 and 6 μm.

- Butterfly-shaped FET: FET with multiple gate fingers to measure S-parameter.

- FATFET: a long gate length FET to measure capacitance.

In addition, the reliability test chip also includes different types of Transmission-Line Method (TLM):

- Standard TLMs:  $W=20 \mu m$ ,  $50 \mu m$ ,  $100 \mu m$ .  $L=2, 3, 4, 10, 20, 30, 40 \mu m$ .

- Special TLMs: W=20  $\mu$ m, 50  $\mu$ m, 100  $\mu$ m. L = 2, 3, 4, 10, 20, 30, 40  $\mu$ m. This pattern can be utilized to measure buffer leakage current. This type of pattern also helps to get a more accurate transfer length ( $L_T$ ) for the Wide Band Gap devices.

Figure 3-2 Layout of the reliability chip used in this work.

Through the utilization of diverse HEMT and TLM variations, we are empowered to analyze the impact of various design elements on reliability. This approach allows us to pinpoint the locations of degradation, identify the primary degradation indicators, and ascertain the crucial factors influencing degradation, such as current and voltage dependencies. This test chip is seamlessly integrated into the standard process development mask. For each production wafer, multiple of these chips are meticulously fabricated. Consequently, we employ these chips from diverse wafers in the comprehensive study conducted at this stage.

## 3.3 Reliability Analysis Methods

# 3.3.1 Interface Trap Density $(D_{ii})$ Extraction

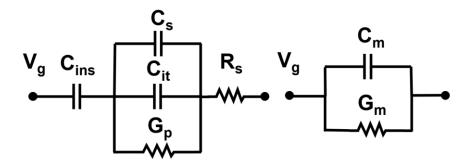

The conductance method is widely used in conventional Si MOSFET devices for the determination of interface trap density  $(D_{it})[82][10]$ . In this process, the interface between the dielectric and the semiconductor is analyzed to identify trap characteristics. In this study, the conductance method was applied to the device structure. The  $Al_xGa_{1-x}N$  barrier layer, characterized by its wide band gap (approximately 4 eV) and high dielectric constant (about 9.4), serves as an insulator, similar to traditional dielectric materials. The focus of the conductance method is on the extraction of the equivalent parallel conductance  $(G_P)$  from the measured frequency-dependent capacitance-voltage (C-V) and conductance-voltage (G-V) characteristics. In Figure 3-3, an equivalent circuit of an AlGaN/GaN HEMT in the depletion region is shown, wherein  $C_{it}$ ,  $C_S$ , and  $R_S$  represent the interface trap capacitance, semiconductor capacitance, and series resistance, respectively.  $C_{it}$  can be expressed as  $C_{it} = qD_{it}$ , where 'q' denotes the elemental charge. The conductance method was effectively utilized to extract interface traps  $(D_{it})[82]$ .

**Figure 3-3** Equivalent circuit diagram representing metal—insulator—semiconductor structure in depletion mode.

This method involves the examination of changes in trap charge states that result in system losses. Traps in closer proximity to the Fermi level ( $E_F$ ) exhibit faster responses due to their lower response time ( $\tau$ ). The formation of interface trap capacitance  $C_{it}$  is directly influenced by electrons captured by interface traps. The evaluation of trap responses is conducted using Shockley-Read-Hall statistics, which take into account capture and emission rates[83][84][85].

$$\tau = \frac{1}{2\pi f} = \frac{1}{\omega} = \frac{e^{\left(\frac{\Delta E}{K_B T}\right)}}{\sigma v_{th} D_{dos}}$$

(3.1)

Here,  $\Delta E$  represents the difference of energy between the trap level  $E_T$  and the majority carrier band edge, either  $E_C$  or  $E_V$ ,  $K_B$  is the Boltzmann constant and T is the temperature. The cross section of traps is represented by  $\sigma$ ,  $v_{th}$  is the average thermal velocity of majority carriers, and  $D_{dos}$  is the effective density of states of the majority carrier band. Figure 3-3 represents the equivalent circuit for analyzing the impedance with measured capacitance  $C_m$  and measured conductance  $G_m$ . These measured values must be corrected for series resistance  $R_s[86]$ :

$$R_{s} = \frac{G_{ma}}{G_{ma}^{2} + \omega^{2} C_{ma}^{2}}$$

(3.2)

Here,  $C_{ma}$  and  $G_{ma}$  are measured capacitance and conductance in the accumulation respectively, and  $\omega$  is the angular frequency.

For the correction of capacitance and parallel equivalent conductance, we can use the following equations[82]:

$$C_{c} = \frac{\left(G_{m}^{2} + \omega^{2} C_{m}^{2}\right) C_{m}}{\left[G_{m} - \left(G_{m}^{2} + \omega^{2} C_{m}^{2}\right) R_{s}\right]^{2} + \omega^{2} C_{m}^{2}}$$

(3.3)

$$G_{c} = \frac{\left(G_{m}^{2} + \omega^{2}C_{m}^{2}\right)\left[G_{m} - \left(G_{m}^{2} + \omega^{2}C_{m}^{2}\right)R_{s}\right]}{\left[G_{m} - \left(G_{m}^{2} + \omega^{2}C_{m}^{2}\right)R_{s}\right]^{2} + \omega^{2}C_{m}^{2}}$$

(3.4)

The equivalent parallel conductance can be measured from the following relation[82]:

$$G_{p} = \frac{\omega^{2} C_{ins}^{2} G_{c}}{G_{c}^{2} + \omega^{2} (C_{ins} - C_{c})^{2}}$$

(3.5)

Here,  $C_{ins}$  is the insulator capacitance. So,  $D_{it}$  can be calculated from the normalized parallel conductance peak  $(G_p/\omega)_{max}[86]$ :

$$D_{it} \approx \frac{2.5}{Aq} \left(\frac{G_p}{\omega}\right)_{\text{max}} \tag{3.6}$$

Here, A is the device area. Eq. 2-1 can be used to determine trap occupancy in the energy level where f is the frequency determined from the conductance peak  $(G_p/\omega)_{max}$  [83].

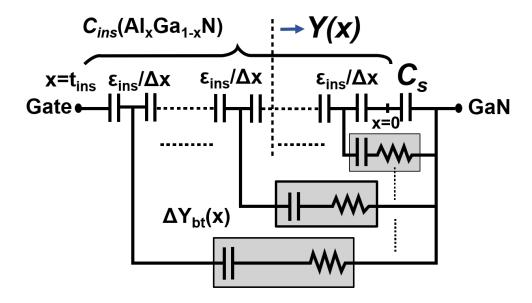

### 3.3.2 Border Trap Density $(N_{bt})$ Extraction

The distributed circuit model shown in Figure 3-4 was used for the extraction of border traps[87]. It can provide information on the border trap states inside the insulator bulk with frequency-dependent C-V measurement.

This model can be represented by the following first-order differential equation [87]:

$$\frac{\partial Y}{\partial x} = -\frac{Y^2}{j\omega\varepsilon_{ins}} + \frac{q^2N_{bt}\ln(1+j\omega\tau)}{\tau}$$

(3.7)

This equation has a boundary condition of x = 0,  $Y = j\omega CS$ , while Y being the total admittance.  $N_{bt}$  in the above equation denotes the density of border traps in the insulator layer.

**Figure 3-4** Equivalent circuit representing distributed bulk-oxide trap model[87].

Usually, the carriers in the channel region and the border traps in the insulator layer can exchange charge through tunneling [87]. The average time ( $\tau$ ) required for an empty trap to capture an electron can be calculated as [88],

$$\tau = \tau_0 e^{2kx} \tag{3.8}$$

Where,

$$k = \frac{\sqrt{2m*\times E_b}}{\hbar}$$

(3.9)

Here,  $\tau_o$  denotes the time constant of the capture and emission of a trap. x denotes the distance between the interface and the trap.  $m^*$  and k denote the effective mass of the  $Al_xGa_{1-x}N$  layer and the attenuation coefficient respectively. The barrier height between the  $Al_xGa_{1-x}N$  and the GaN channel conduction band is denoted by  $E_b$  and the reduced Plank's constant by  $\hbar$ .

$\tau_o$  can be characterized as

$$\tau_{\circ} = \left(n_{s} v_{th} \sigma\right)^{-1} \tag{3.10}$$

Where,  $n_s$ ,  $v_{th}$ , and  $\sigma$  are the electron density of the channel surface, the average thermal velocity of the electron, and the border trap cross-section area of capture/emission, respectively. Equation 3.7, can be simplified into the following equation for the total capacitance,  $C_{tot}[89]$ ,

$$C_{tot} = \frac{1}{\frac{1}{C_{ins}} + \frac{1}{2k\varepsilon_{ins}}} C_2(\omega)$$

(3.11)

$$C_2(\omega) = 2k \sqrt{\frac{\varepsilon_{ins}}{qN_{bt}}} \coth(B) + \ln(\omega \tau_o) - \coth^2(B)$$

(3.12)

$$B = a \tanh\left(\sqrt{\frac{1}{qN_{bt}}\varepsilon_{ins}}C_{s}\right) - \frac{1}{2k}\sqrt{\frac{qN_{bt}}{\varepsilon_{ins}}}\ln(\omega\tau_{o})$$

(3.13)